V61C31161024

Features s s s s s High-speed: 10, 12, 15 ns All inputs and outputs directly TTL patible Three state outputs Single 3.3V ± 10% Power Supply Packages

- 44-pin TSOP (Standard)

- 44-pin 400 mil SOJ s Low Power Consumption

- Active: 140m A

- Standby: 2m A (CMOS)

Description

The V61C31161024 is a 1,048,576-bit static random-access memory organized as 65,536 words by 16 bits. Inputs and three-state outputs are TTL patible and allow for direct interfacing with mon system bus structures.

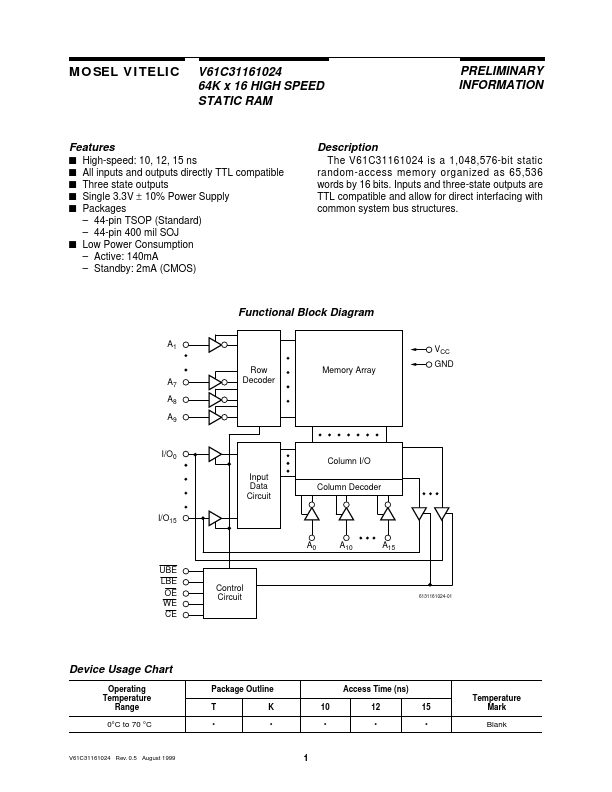

Functional Block Diagram

A1 Row Decoder Memory Array VCC GND

A7 A8 A9

I/O0 Input Data Circuit I/O15 A0 UBE LBE OE WE CE

Column I/O Column Decoder

A10

A15

Control Circuit

6131161024-01

Device Usage Chart

Operating Temperature Range 0°C to 70 °C Package Outline T

- K

- 10

- Access Time (ns) 12

- 15

- Temperature Mark Blank

V61C31161024 Rev. 0.5 August 1999

MOSEL VITELIC

Pin Descriptions

A0- A15 Address Inputs These 16 address inputs select one of the 64K x 16 bit segments in the RAM. CE Chip Enable...