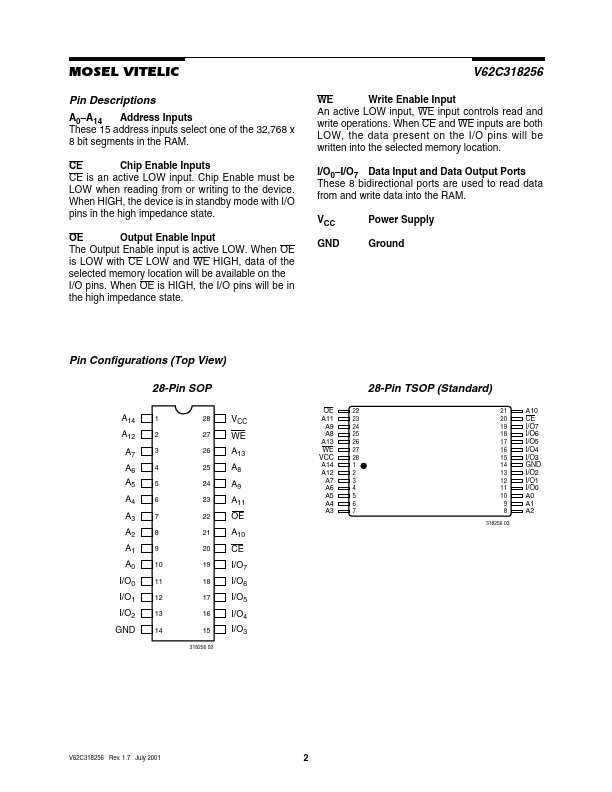

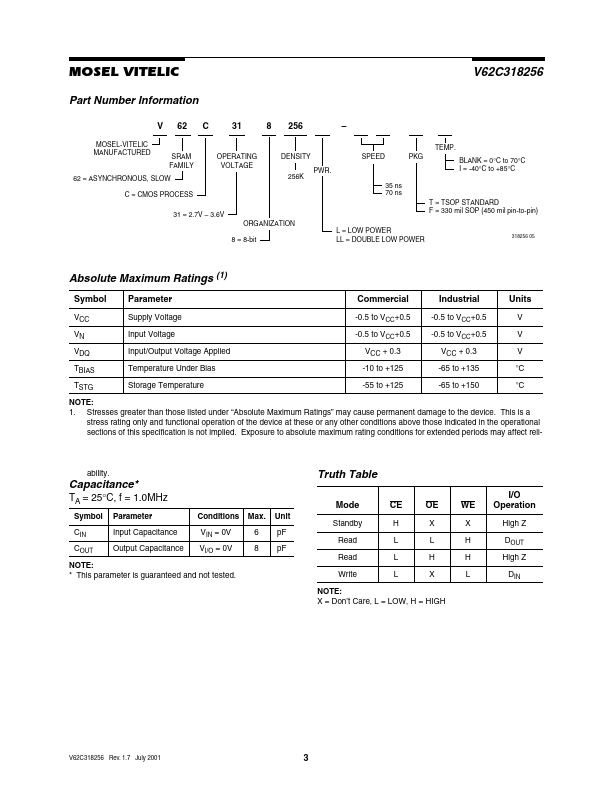

Datasheet Summary

MOSEL VITELIC

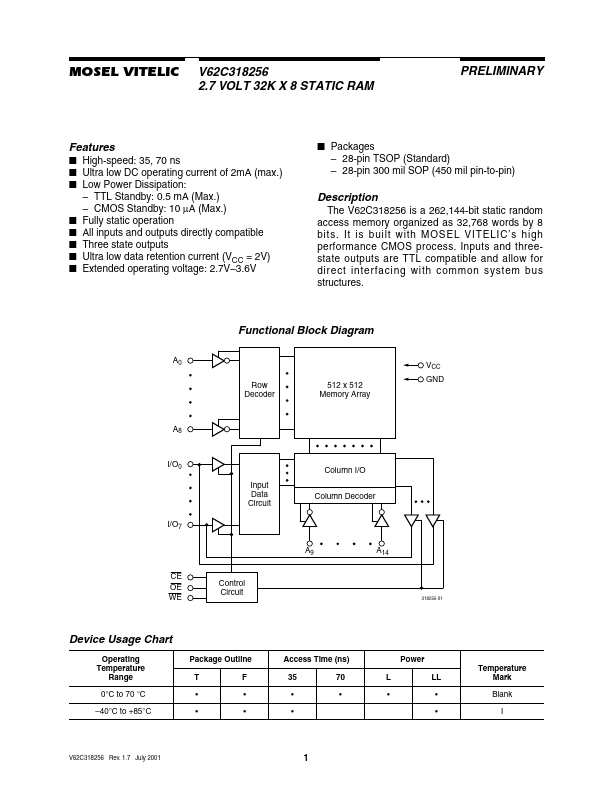

V62C318256 2.7 VOLT 32K X 8 STATIC RAM

PRELIMINARY

Features

I High-speed: 35, 70 ns I Ultra low DC operating current of 2mA (max.) I Low Power Dissipation:

- TTL Standby: 0.5 mA (Max.)

- CMOS Standby: 10 µA (Max.) I Fully static operation I All inputs and outputs directly patible I Three state outputs I Ultra low data retention current (VCC = 2V) I Extended operating voltage: 2.7V- 3.6V

I Packages

- 28-pin TSOP (Standard)

- 28-pin 300 mil SOP (450 mil pin-to-pin)

Description

The V62C318256 is a 262,144-bit static random access memory organized as 32,768 words by 8 bits. It is built with MOSEL VITELIC’s high performance CMOS process. Inputs and threestate outputs are...