| Part | SN54LS74A |

|---|---|

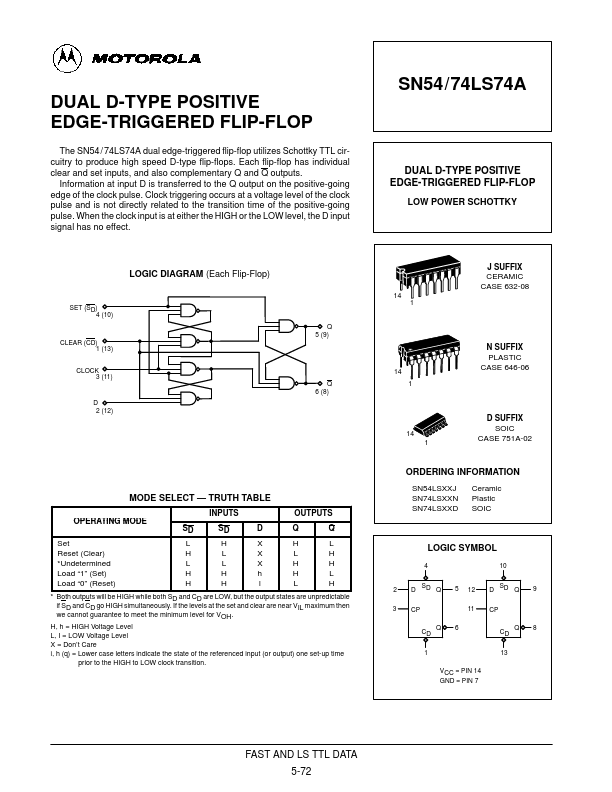

| Description | DUAL D-TYPE POSITIVE EDGE-TRIGGERED FLIP-FLOP |

| Manufacturer | Motorola Semiconductor |

| Size | 73.40 KB |

Pricing from 14.917 USD, available from Texas Instruments and Win Source.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Texas Instruments | 0 | 1+ : 14.917 USD 100+ : 13.03 USD 250+ : 10.046 USD 1000+ : 8.986 USD |

View Offer |

| Win Source | 1975 | 3+ : 20.77 USD 6+ : 17.0421 USD 10+ : 16.5095 USD 13+ : 15.977 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| SN54LS74A | Texas Instruments | Dual D-Type Positive-Edge Triggered Flip-Flops |

| SN54LS748 | Motorola Semiconductor | 10-LINE-TO-4-LINE AND 8-LINE-TO-3-LINE PRIORITY ENCODERS |

| SN54LS75 | Texas Instruments | 4-BIT BISTABLE LATCHE |

| SN54LS76A | Texas Instruments | DUAL J-K FLIP-FLOPS |

| SN54LS73A | Texas Instruments | DUAL J-K FLIP-FLOPS |