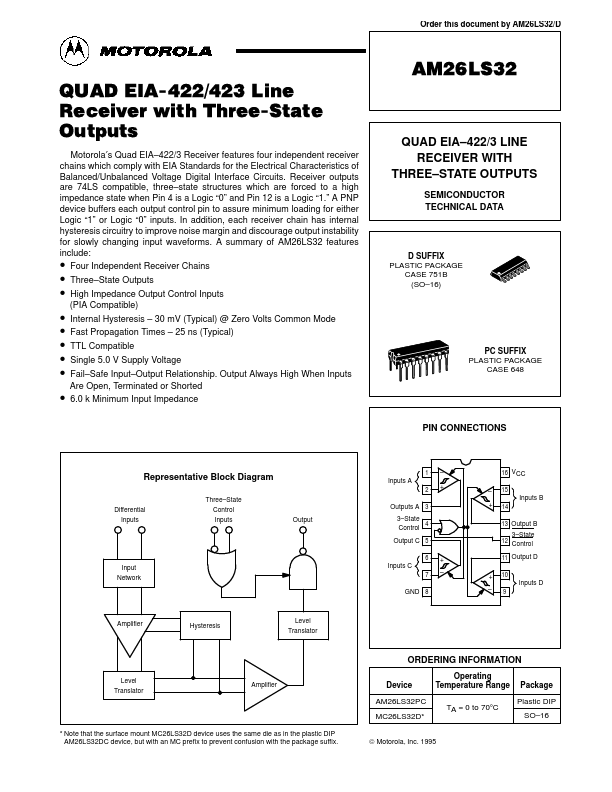

| Part | 26LS32 |

|---|---|

| Description | 3-LINE RECEIVER |

| Manufacturer | Motorola Semiconductor |

| Size | 81.17 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 26LS32A | Texas Instruments | Quadruple Differential Line Receivers |

| 26LS32-SMD | SYC | Quad Differential Line Receivers |

| 26LS32AI | Texas Instruments | Quadruple Differential Line Receivers |

| 26LS32AC | Texas Instruments | Quadruple Differential Line Receivers |

| 26LS31 | NationalSemiconductor | Quad High Speed Differential Line Driver |