Datasheet Summary

..

Semiconductor Products Sector

DSP56F826/D Rev. # 0, 3/2001

Preliminary Technical Data

DSP56F826 16-bit Digital Signal Processor

- -

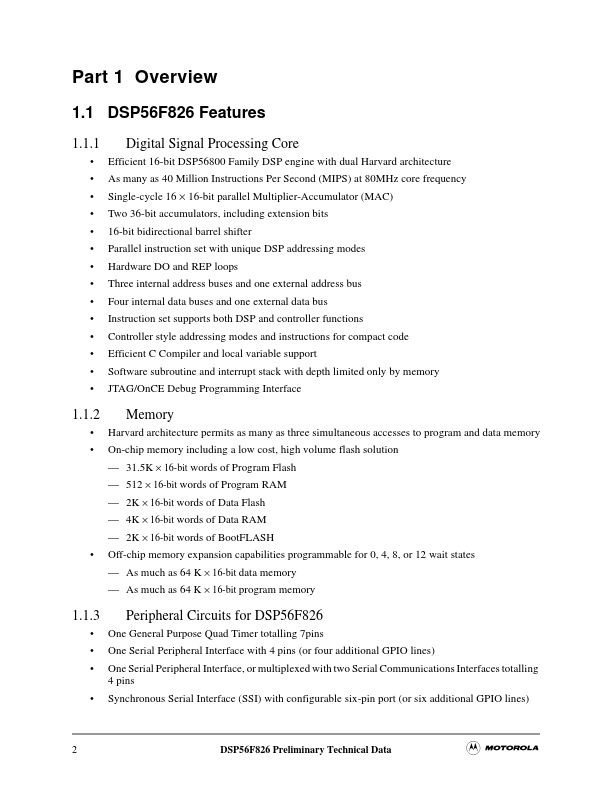

- - Up to 40 MIPS at 80MHz core frequency DSP and MCU functionality in a unified, C-efficient architecture Hardware DO and REP loops MCU-friendly instruction set supports both DSP and controller functions: MAC, bit manipulation unit, 14 addressing modes 31.5K × 16-bit words Program Flash 512 × 16-bit words Program RAM 2K × 16-bit words Data Flash 4K × 16-bit words Data RAM 2K × 16-bit words BootFLASH

EXTBOOT RESET IRQA IRQB 6 JTAG/ OnCE Port TOD Timer Interrupt Controller Program Controller and Hardware Looping Unit Address...