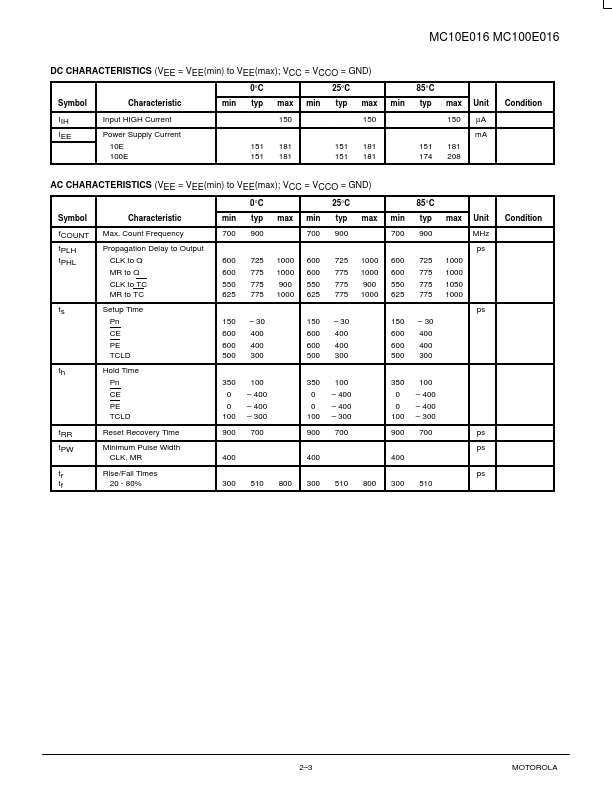

Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

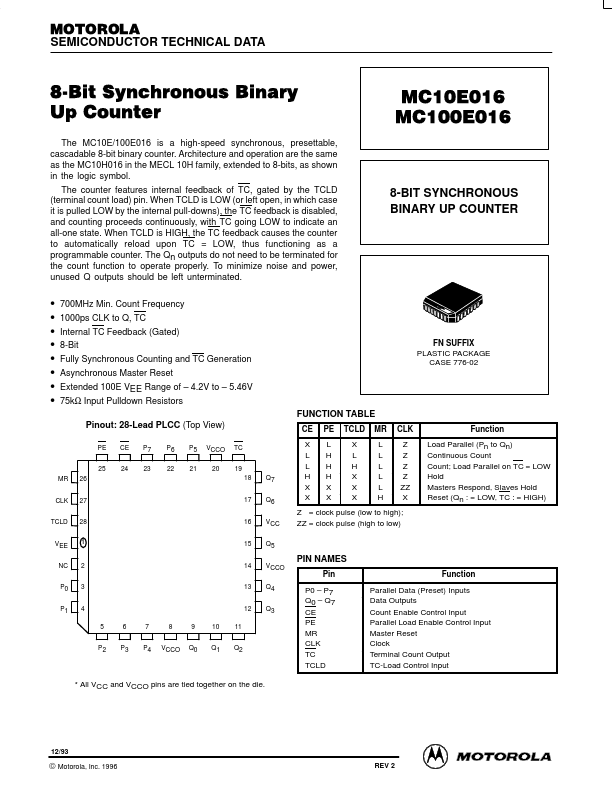

8ĆBit Synchronous Binary Up Counter

MC10E016 MC100E016

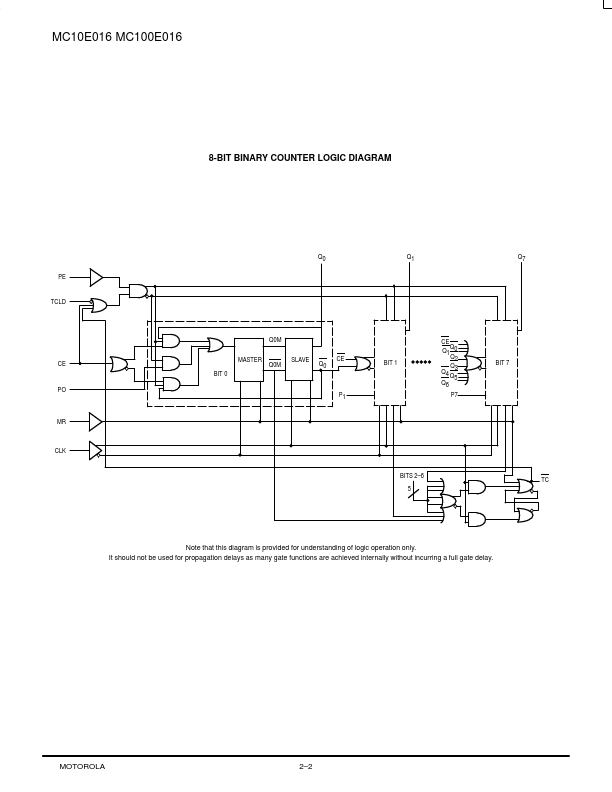

The MC10E/100E016 is a high-speed synchronous, presettable, cascadable 8-bit binary counter. Architecture and operation are the same as the MC10H016 in the MECL 10H family, extended to 8-bits, as shown in the logic symbol.

The counter Features internal feedback of TC, gated by the TCLD (terminal count load) pin. When TCLD is LOW (or left open, in which case it is pulled LOW by the internal pull-downs), the TC feedback is disabled, and counting proceeds continuously, with TC going LOW to indicate an all-one state. When TCLD is HIGH, the TC feedback causes the counter to automatically reload upon...