MC10107

MC10107 is Triple 2-Input Exclusive OR/Exclusive NOR Gate manufactured by Motorola Semiconductor.

- Part of the MC10107L comparator family.

- Part of the MC10107L comparator family.

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

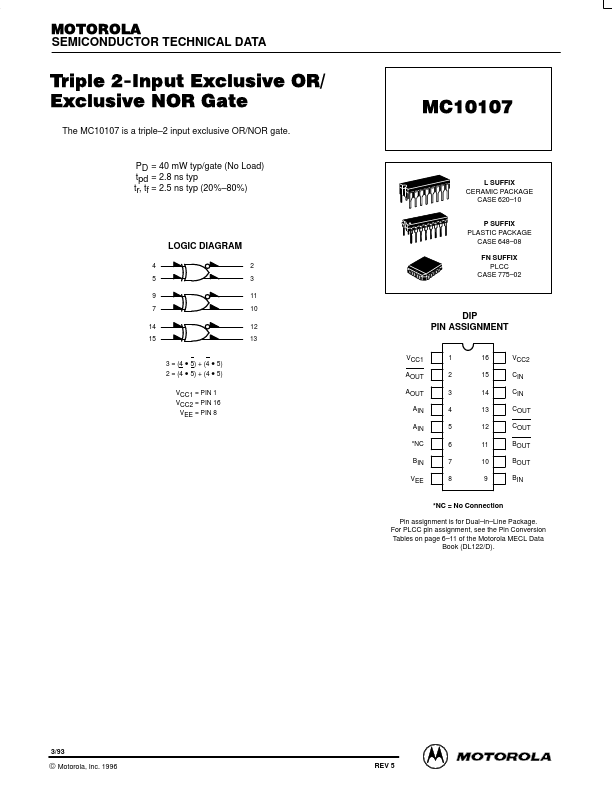

Triple 2-Input Exclusive OR/ Exclusive NOR Gate

The MC10107 is a triple- 2 input exclusive OR/NOR gate.

PD = 40 m W typ/gate (No Load) tpd = 2.8 ns typ tr, tf = 2.5 ns typ (20%- 80%)

LOGIC DIAGRAM 42 53 9 11 7 10 14 12 15 13

3 = (4

- 5) + (4

- 5) 2 = (4

- 5) + (4

- 5)

VCC1 = PIN 1 VCC2 = PIN 16

VEE = PIN 8

L SUFFIX CERAMIC PACKAGE

CASE 620- 10

P SUFFIX PLASTIC PACKAGE

CASE 648- 08

FN SUFFIX PLCC

CASE 775- 02

DIP PIN ASSIGNMENT

VCC1 AOUT AOUT

AIN AIN

- NC

BIN VEE

1 2 3 4 5 6 7 8

16 VCC2 15 CIN 14 CIN 13 COUT 12 COUT 11 BOUT 10 BOUT 9 BIN

- NC = No Connection

Pin assignment is for Dual- in- Line Package. For PLCC pin assignment, see the Pin Conversion Tables on page 6- 11 of the Motorola MECL Data

Book (DL122/D).

3/93

© Motorola, Inc. 1996

3- 30

REV 5

ELECTRICAL CHARACTERISTICS

Characteristic

Symbol

Pin Under Test

- 30°C Min Max

Power Supply Drain Current Input Current

IE...