MC10H645

features a 24m A TTL ouput stage with AC performance specified into a 50p F load capacitance. A 2:1 input mux is provided on chip to allow for distributing both system and diagnostic clock signals or designing clock redundancy into a system. With the SEL input held LOW the DO input will be selected, while the D1 input is selected when the SEL input is forced HIGH.

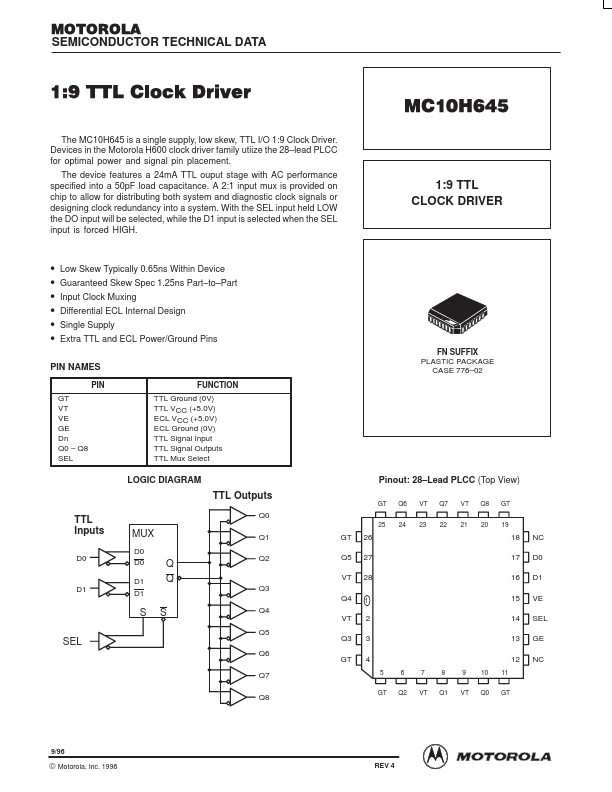

1:9 TTL CLOCK DRIVER

- Low Skew Typically 0.65ns Within Device

- Guaranteed Skew Spec 1.25ns Part- to- Part

- Input Clock Muxing

- Differential ECL Internal Design

- Single Supply

- Extra TTL and ECL Power/Ground Pins

PIN NAMES PIN

GT VT VE GE Dn Q0

- Q8 SEL

TTL Inputs

D0

D1

FUNCTION

TTL Ground (0V) TTL VCC (+5.0V) ECL VCC (+5.0V) ECL...