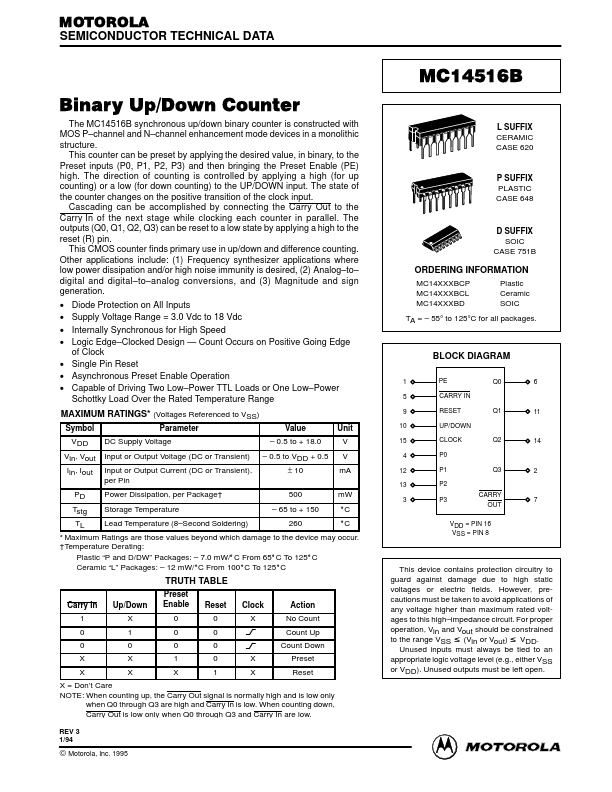

| Part | MC14516B |

|---|---|

| Description | Binary Up/Down Counter |

| Manufacturer | Motorola Semiconductor |

| Size | 258.18 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MC145163 | Unknown Manufacturer | MC145163 PLL Integrated Circuits |

| MC1451A | PMD | Advanced Step Motor Control Chipset |