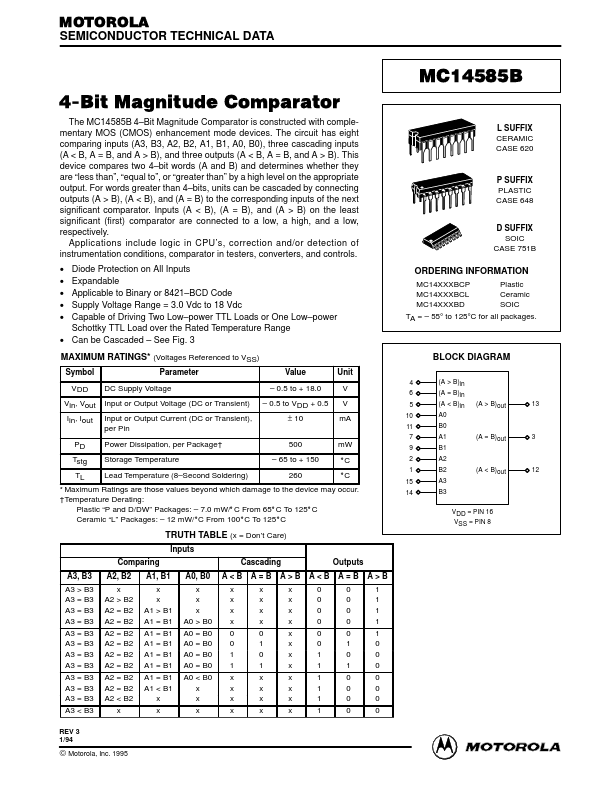

MC14585B

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

MC14585B 4-Bit Magnitude parator

The MC14585B 4- Bit Magnitude parator is constructed with plementary MOS (CMOS) enhancement mode devices. The circuit has eight paring inputs (A3, B3, A2, B2, A1, B1, A0, B0), three cascading inputs (A < B, A = B, and A > B), and three outputs (A < B, A = B, and A > B). This device pares two 4- bit words (A and B) and determines whether they are “less than”, “equal to”, or “greater than” by a high level on the appropriate output. For words greater than 4- bits, units can be cascaded by connecting outputs (A > B), (A < B), and (A = B) to the corresponding inputs of the next significant parator. Inputs (A < B), (A = B), and (A > B) on the least significant (first) parator are connected to a low, a high, and a low, respectively. Applications include logic in CPU’s, correction and/or detection of instrumentation conditions, parator in testers, converters, and controls.

- -

- -

- Diode Protection on All Inputs Expandable...