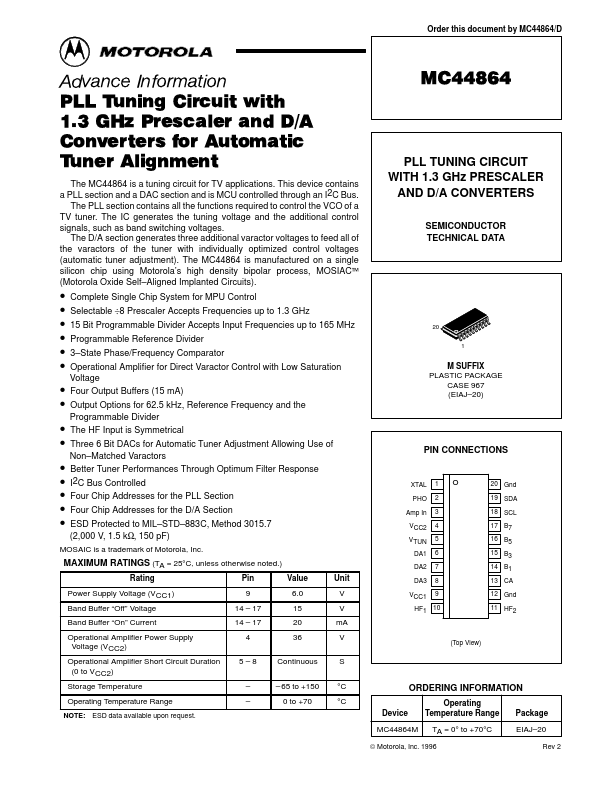

MC44864

MC44864 is PLL TUNING CIRCUIT manufactured by Motorola Semiconductor.

Order this document by MC44864/D

Advance Information

PLL Tuning Circuit with 1.3 GHz Prescaler and D/A Converters for Automatic Tuner Alignment

The MC44864 is a tuning circuit for TV applications. This device contains a PLL section and a DAC section and is MCU controlled through an I2C Bus. The PLL section contains all the functions required to control the VCO of a TV tuner. The IC generates the tuning voltage and the additional control signals, such as band switching voltages. The D/A section generates three additional varactor voltages to feed all of the varactors of the tuner with individually optimized control voltages (automatic tuner adjustment). The MC44864 is manufactured on a...