MC74HC73

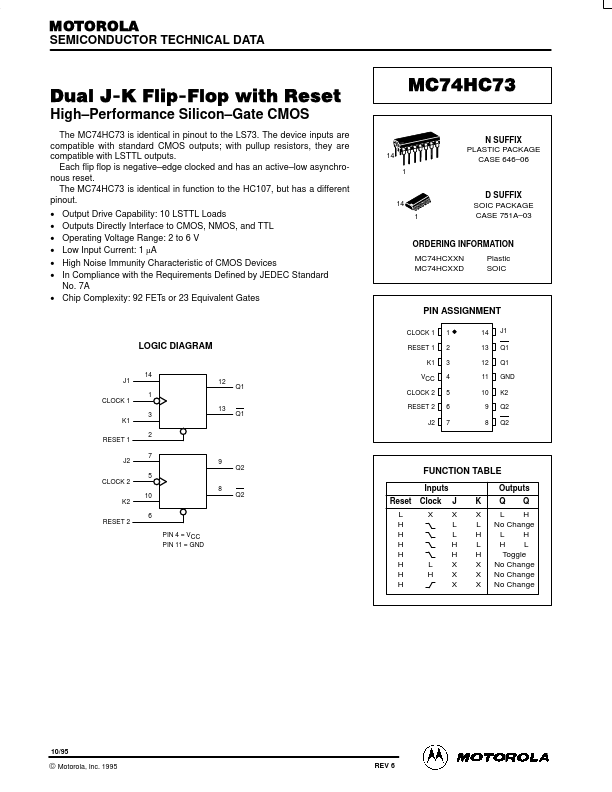

MC74HC73 is Dual J-K Flip-Flop manufactured by Motorola Semiconductor.

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Dual J-K Flip-Flop with Reset

High- Performance Silicon- Gate CMOS

The MC74HC73 is identical in pinout to the LS73. The device inputs are patible with standard CMOS outputs; with pullup resistors, they are patible with LSTTL outputs. Each flip flop is negative- edge clocked and has an active- low asynchronous reset. The MC74HC73 is identical in function to the HC107, but has a different pinout.

- -

- -

- - Output Drive Capability: 10 LSTTL Loads Outputs Directly Interface to CMOS, NMOS, and TTL Operating Voltage Range: 2 to 6 V Low Input Current: 1 µA High Noise Immunity Characteristic of CMOS Devices In pliance with the Requirements Defined by...