MC75HC107 Description

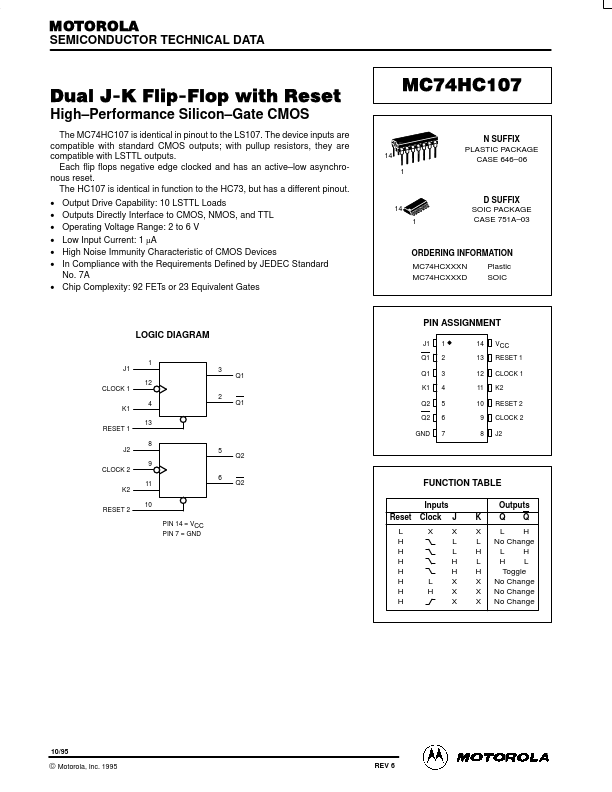

MOTOROLA SEMICONDUCTOR TECHNICAL DATA Dual J-K Flip-Flop with Reset High Performance Silicon Gate CMOS The MC74HC107 is identical in pinout to the LS107. The device inputs are patible with standard CMOS outputs; with pullup resistors, they are patible with LSTTL outputs.