MC92300

MC92300 is VITERBI Decoder for Digital TV manufactured by Motorola Semiconductor.

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Current Information@.mot./ADC

Product Preview

VITERBI Decoder for Digital TV

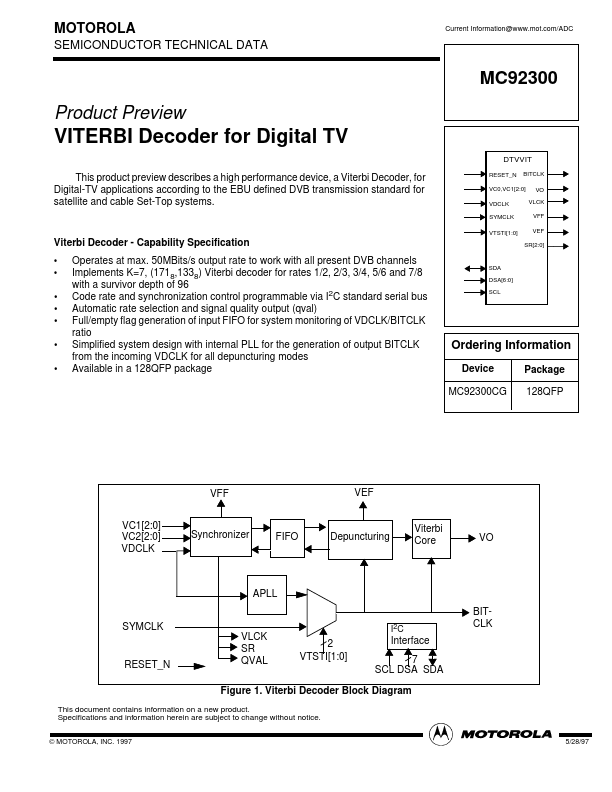

DTVVIT

This product preview describes a high performance device, a Viterbi Decoder, for Digital-TV applications according to the EBU defined DVB transmission standard for satellite and cable Set-Top systems.

RESET_N

BITCLK VO VLCK VFF VEF SR[2:0]

VC0,VC1[2:0] VDCLK SYMCLK VTSTI[1:0]

Viterbi Decoder

- Capability Specification

- -

- -

- -

- Operates at max. 50MBits/s output rate to work with all present DVB channels Implements K=7, (1718,1338) Viterbi decoder for rates 1/2, 2/3, 3/4, 5/6 and 7/8 with a survivor depth of 96 Code rate and synchronization...