MCM62110 Description

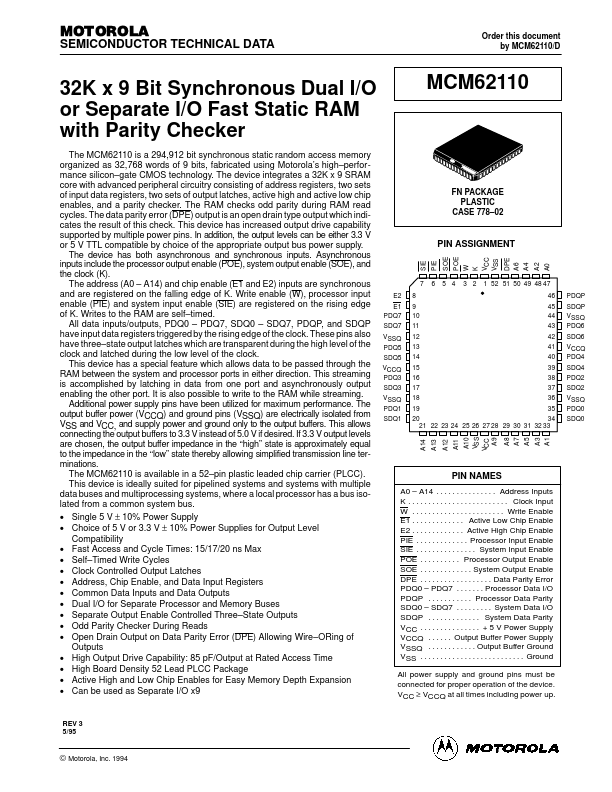

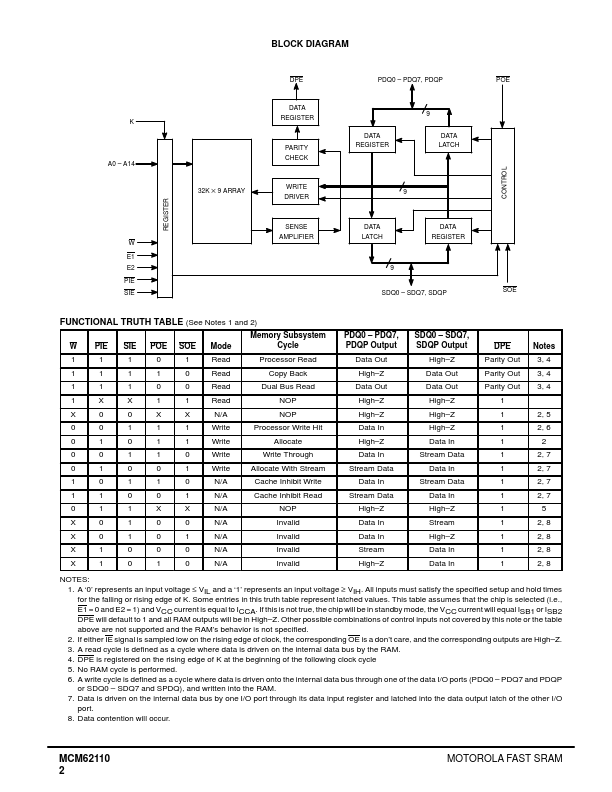

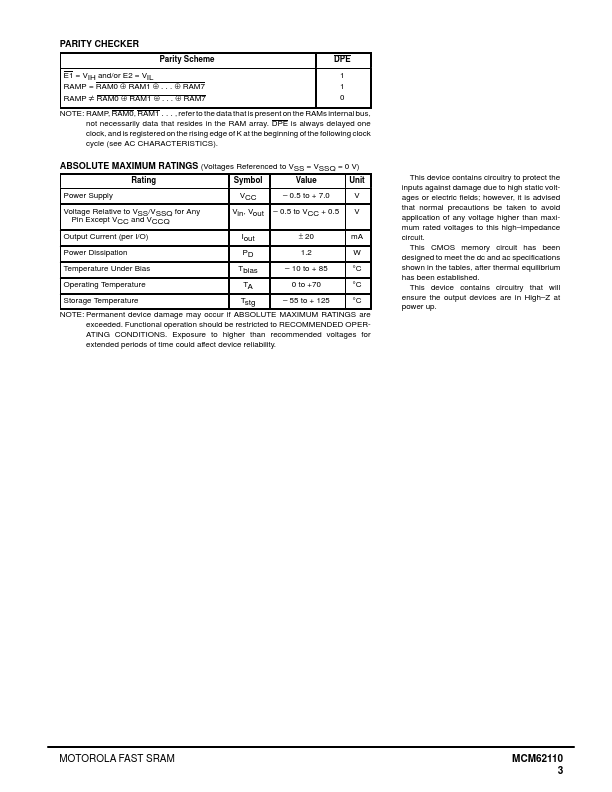

MOTOROLA SEMICONDUCTOR TECHNICAL DATA Order this document by MCM62110/D 32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker The MCM62110 is a 294,912 bit synchronous static random access memory organized as 32,768 words of 9 bits, fabricated using Motorola’s high performance silicon gate CMOS technology. The device integrates a 32K x 9 SRAM core with advanced peripheral circuitry...