MCM6229BB

MCM6229BB is 256K x 4 Bit Static Random Access Memory manufactured by Motorola Semiconductor.

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MCM6229BB/D

Product Preview

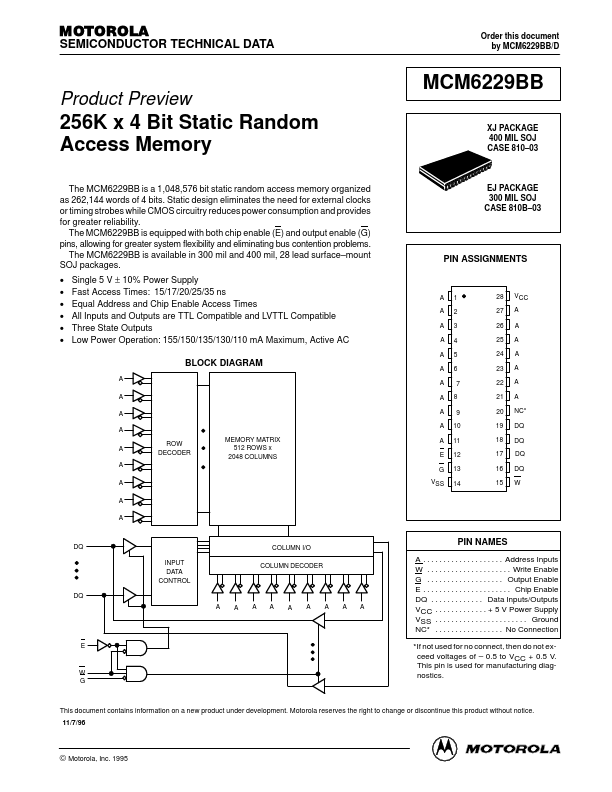

XJ PACKAGE 400 MIL SOJ CASE 810- 03

256K x 4 Bit Static Random Access Memory

The MCM6229BB is a 1,048,576 bit static random access memory organized as 262,144 words of 4 bits. Static design eliminates the need for external clocks or timing strobes while CMOS circuitry reduces power consumption and provides for greater reliability. The MCM6229BB is equipped with both chip enable (E) and output enable (G) pins, allowing for greater system flexibility and eliminating bus contention problems. The MCM6229BB is available in 300 mil and 400 mil, 28 lead surface- mount SOJ packages.

- -

- -

- -...