MCM62Y308 Description

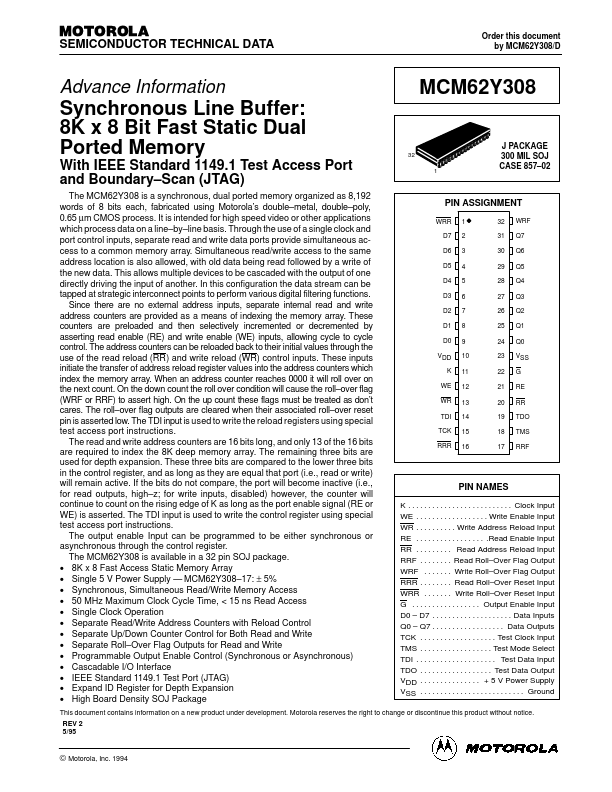

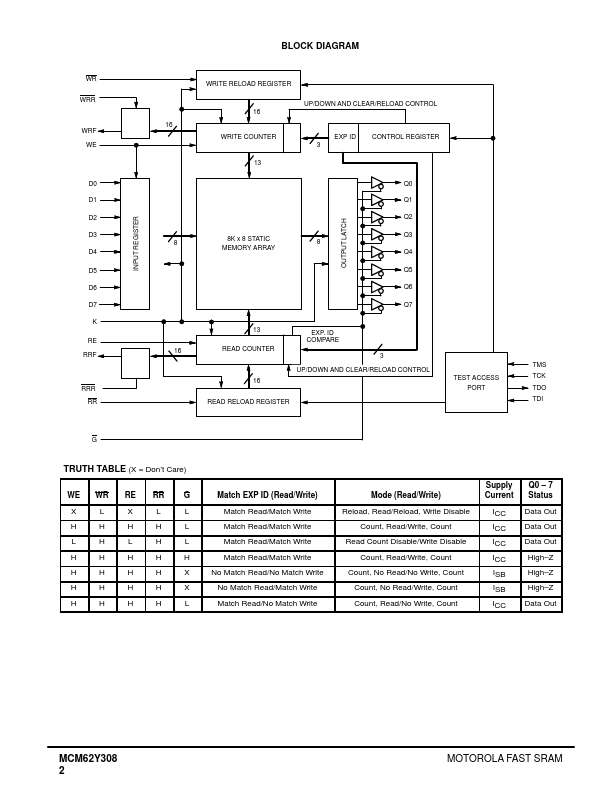

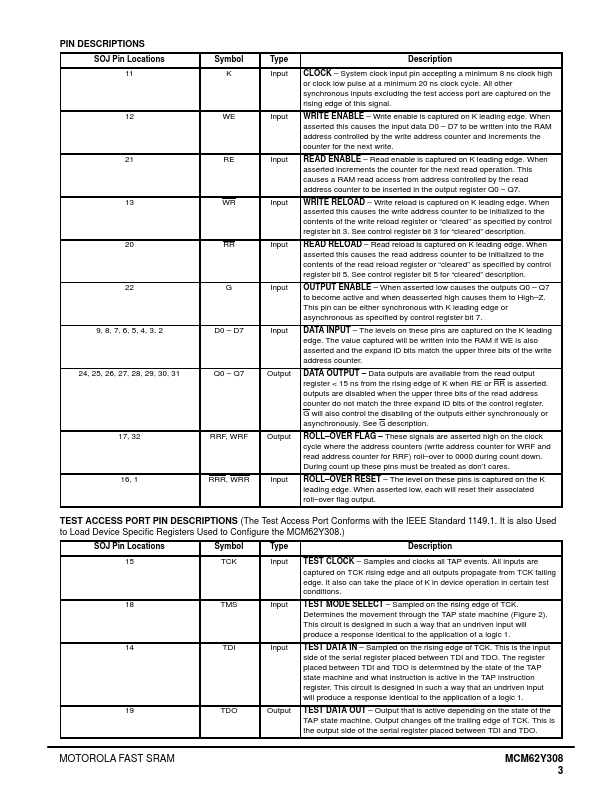

MOTOROLA SEMICONDUCTOR TECHNICAL DATA Order this document by MCM62Y308/D Advance Information MCM62Y308 J PACKAGE 300 MIL SOJ CASE 857 02 Synchronous Line Buffer: 8K x 8 Bit Fast Static Dual Ported Memory With IEEE Standard 1149.1 Test Access Port and Boundary Scan (JTAG) The MCM62Y308 is a synchronous, dual ported memory organized as 8,192 words of 8 bits each, fabricated using Motorola’s double metal, double poly,...