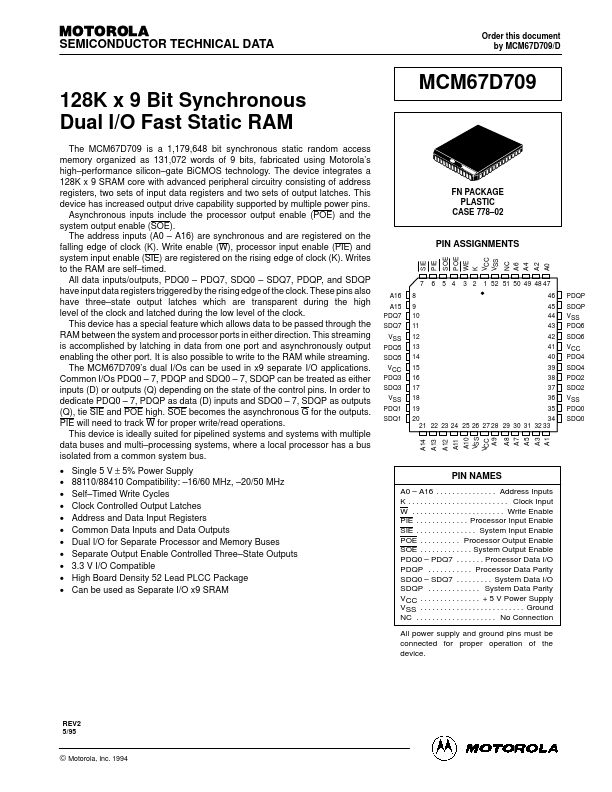

- Part: MCM67D709

- Description: 128K x 9 Bit Synchronous Dual I/O Fast Static RAM

- Manufacturer: Motorola Semiconductor

- Size: 176.00 KB

Related Motorola Semiconductor Datasheets

| Part Number | Description |

|---|---|

| MCM6706A | 32K x 8 Bit Static Random Access Memory |

| MCM6706AR | 32K x 8 Bit Static Random Access Memory |

| MCM6706B | 32K x 8 Bit Static Random Access Memory |

| MCM6706BR | 32K x 8 Bit Static Random Access Memory |

| MCM6706CR | 32K x 8 Bit Static Random Access Memory |