MCM67F804 Overview

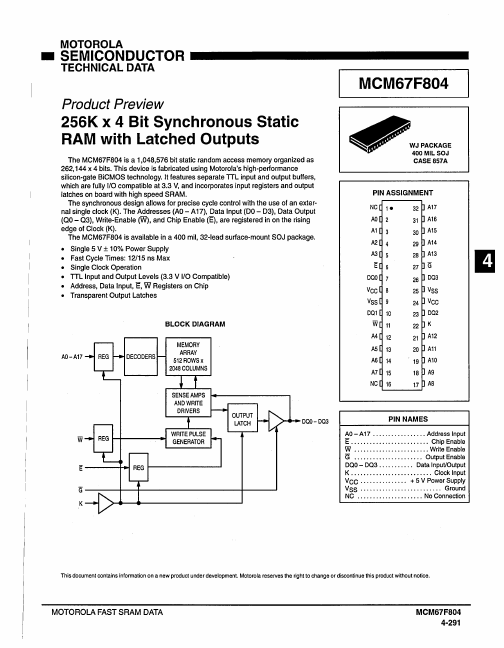

MOTOROLA SEMICONDUCTOR TECHNICAL DATA Product Preview 256K x 4 Bit Synchronous Static RAM with Latched Outputs The MCM67F804 is a 1,048,576 bit static random access memory organized as 262,144 x 4 bits. This device is fabricated using Motorola's high-performance silicon-gate BiCMOS technology.

MCM67F804 Key Features

- A17), Data Input (DO

- D3), Data Output (00

- 03), Write-Enable (W), and Chip Enable (E), are registered in on the rising edge of Clock (K)

- Single 5 V ± 10% Power Supply

- Fast Cycle Times: 12115 ns Max

- Single Clock Operation

- TTL Input and Output Levels (3.3 V I/O patible)

- Address, Data Input, E, WRegis