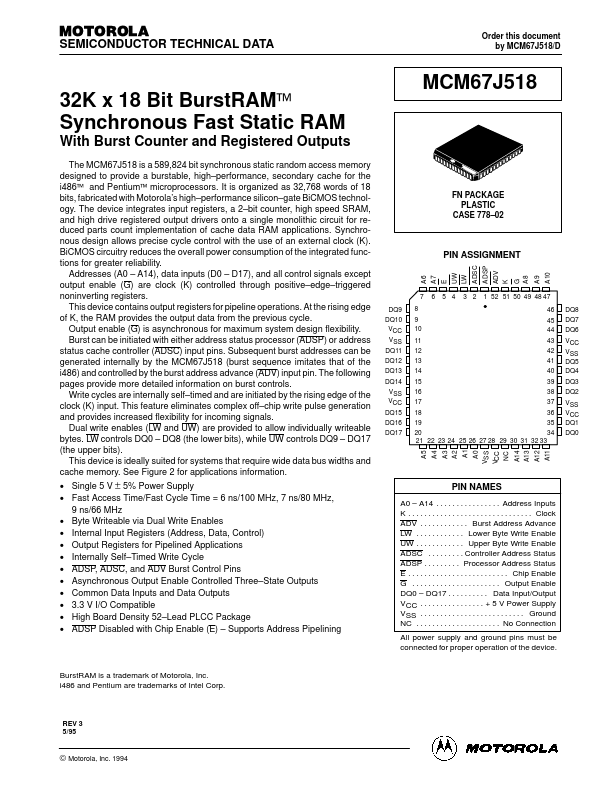

MCM67J518

Key Features

- Single 5 V ± 5% Power Supply

- Fast Access Time/Fast Cycle Time = 6 ns/100 MHz, 7 ns/80 MHz, 9 ns/66 MHz

- Internal Input Registers (Address, Data, Control)

- Output Registers for Pipelined Applications

- Internally Self–Timed Write Cycle

- ADSP, ADSC, and ADV Burst Control Pins

- Asynchronous Output Enable Controlled Three–State Outputs

- mon Data Inputs and Data Outputs

- 3.3 V I/O compatible

- High Board Density 52–Lead PLCC Package