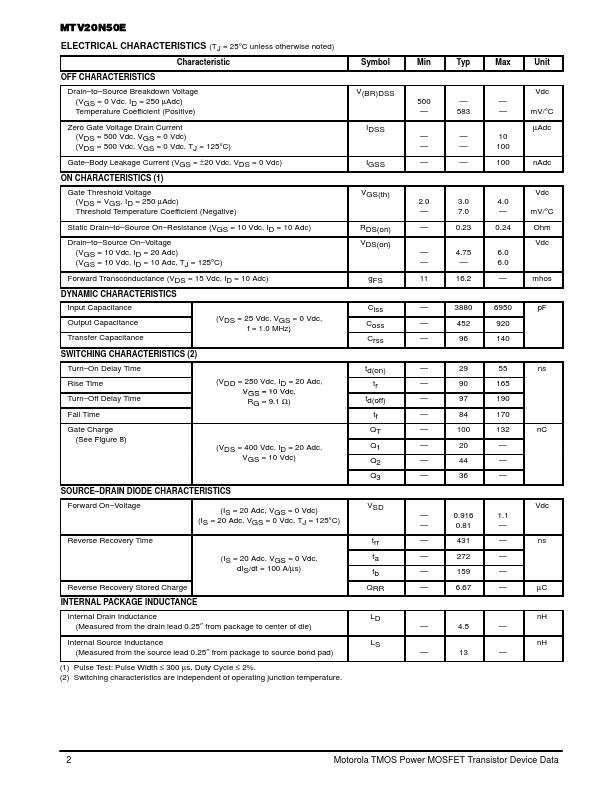

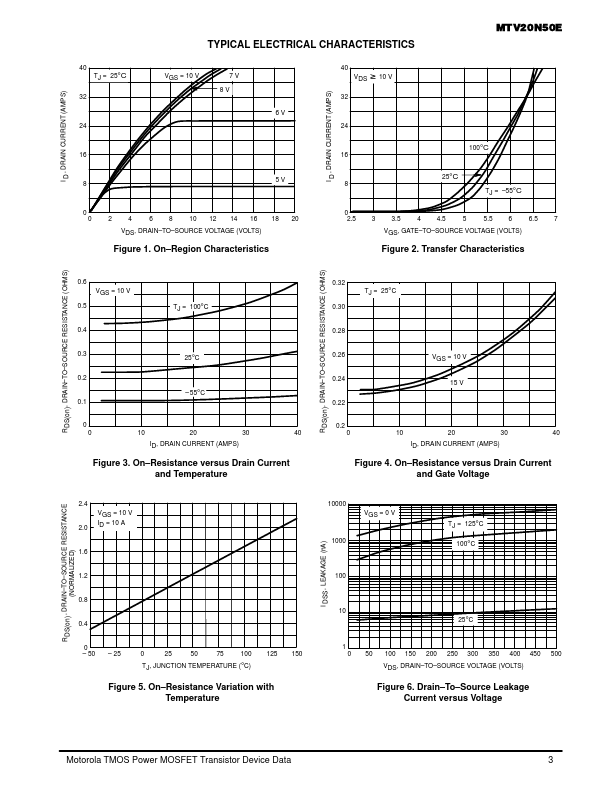

Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MTV20N50E/D

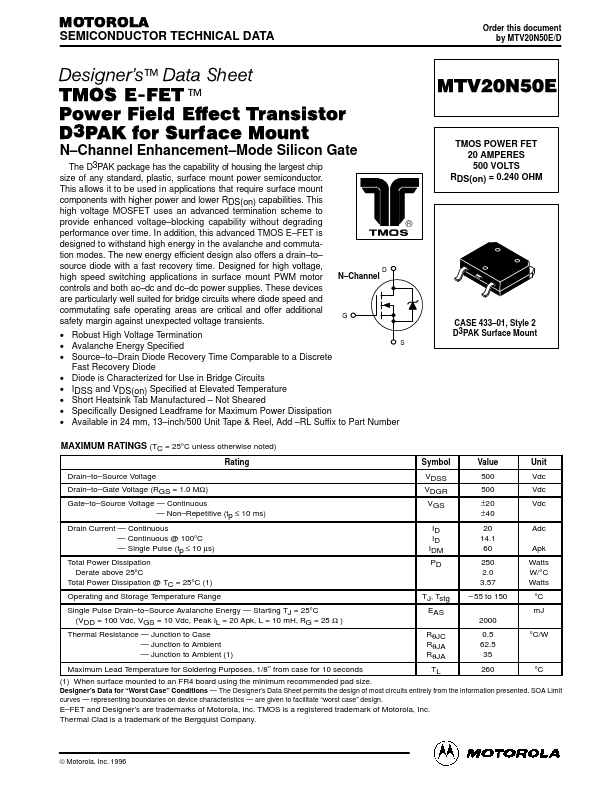

™ Data Sheet TMOS E-FET.™ Power Field Effect Transistor D3PAK for Surface Mount

Designer's

TMOS POWER FET 20 AMPERES 500 VOLTS RDS(on) = 0.240 OHM

N- Channel Enhancement- Mode Silicon Gate

The D3PAK package has the capability of housing the largest chip size of any standard, plastic, surface mount power semiconductor. This allows it to be used in applications that require surface mount ponents with higher power and lower RDS(on) capabilities. This high voltage MOSFET uses an advanced termination scheme to provide enhanced voltage- blocking capability without degrading performance over time. In addition,...