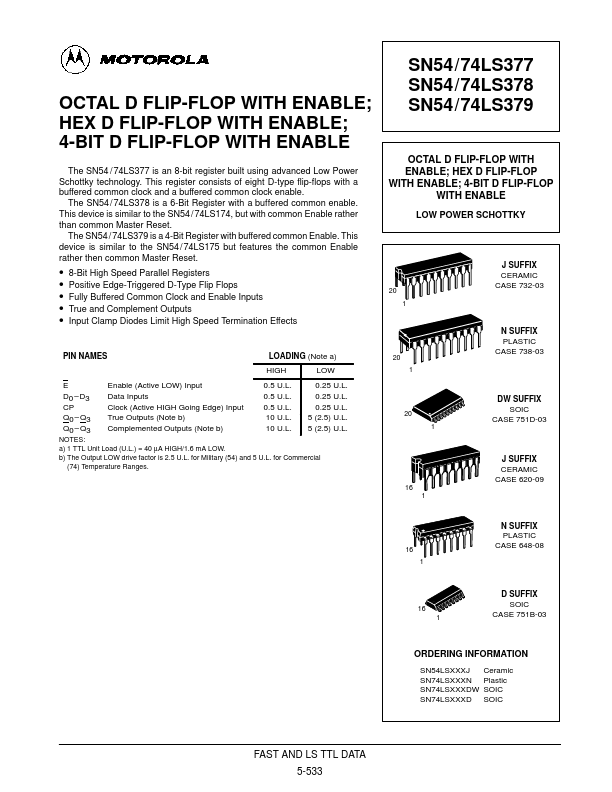

- Part: SN54LS379

- Description: OCTAL D FLIP-FLOP

- Manufacturer: Motorola Semiconductor

- Size: 250.77 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| SN54LS375 | Motorola Semiconductor | 4-BIT D LATCH |

| SN54LS373 | Texas Instruments | OCTAL D-TYPE TRANSPARENT LATCHES AND EDGE-TRIGGERED FLIP-FLOPS |

| SN54LS375 | Texas Instruments | 4-Bit Bistable Latches |