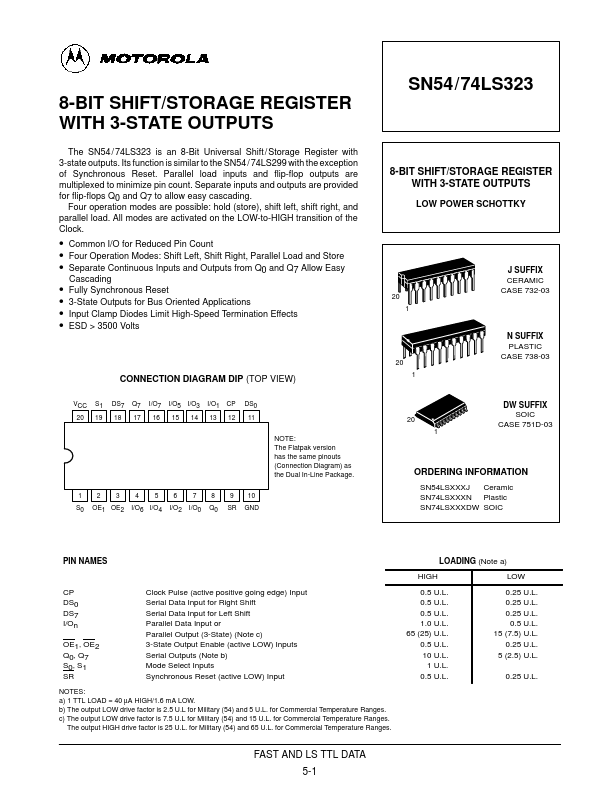

| Part | SN74LS323 |

|---|---|

| Description | 8-BIT SHIFT/STORAGE REGISTER |

| Manufacturer | Motorola Semiconductor |

| Size | 137.59 KB |

Pricing from 1.56 USD, available from Rochester Electronics and Verical.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 6000 | 100+ : 1.56 USD 500+ : 1.4 USD 1000+ : 1.29 USD 10000+ : 1.15 USD |

View Offer |

| Verical | 6000 | 193+ : 1.95 USD 500+ : 1.75 USD 1000+ : 1.6125 USD 10000+ : 1.4375 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| SN74LS32 | onsemi | Quad 2-Input OR Gate |

| SN74LS32 | Texas Instruments | Quadruple 2-Input Positive-OR Gates |

| SN74LS320 | Texas Instruments | CRYSTAL-CONTROLLED OSCILLATORS |

| SN74LS321 | Texas Instruments | CRYSTAL-CONTROLLED OSCILLATORS |