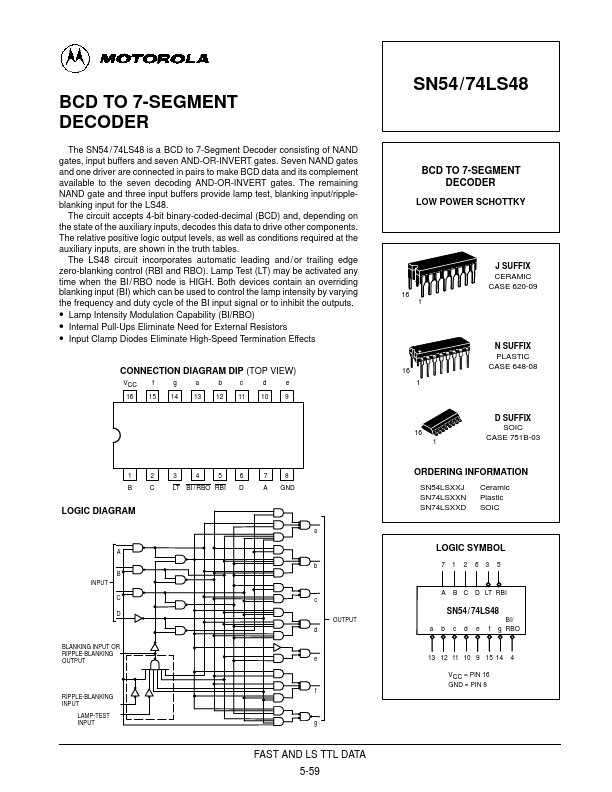

| Part | SN74LS48 |

|---|---|

| Description | BCD TO 7-SEGMENT DECODER |

| Manufacturer | Motorola Semiconductor |

| Size | 100.33 KB |

Pricing from 0.329 USD, available from Verical and Rochester Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Verical | 1302 | 1140+ : 0.329 USD 10000+ : 0.2934 USD 100000+ : 0.2458 USD |

View Offer |

| Rochester Electronics | 1302 | 100+ : 0.3171 USD 500+ : 0.2854 USD 1000+ : 0.2632 USD 10000+ : 0.2347 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| SN74LS48 | Texas Instruments | BCD-TO-SEVEN-SEGMENT DECODERS/DRIVERS |

| SN74LS47N | onsemi | BCD to 7-Segment Decoder/Driver |

| SN74LS47D | Texas Instruments | BCD-TO-SEVEN-SEGMENT DECODERS/DRIVERS |

| SN74LS47D | onsemi | BCD to 7-Segment Decoder/Driver |

| SN74LS47 | onsemi | BCD to 7-Segment Decoder/Driver |