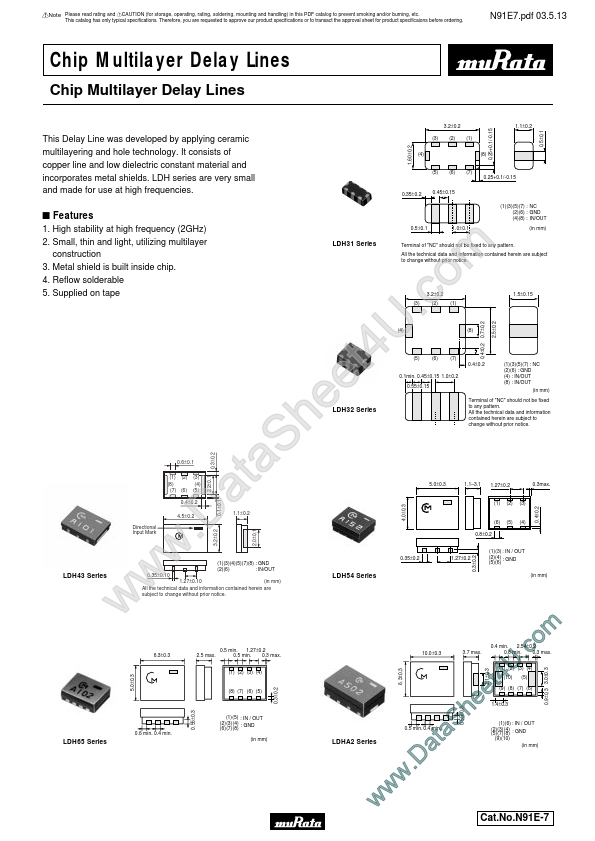

LDH43100PAAA-830

Overview

- High stability at high frequency (2GHz)

- 5±0.1

- 0±0.1 (in mm)

- Small, thin and light, utilizing multilayer construction m3. Metal shield is built inside chip.

- Reflow solderable o5. Supplied on tape Sheet4U.c0.6±0.1 .DataDirectional Input Mark (1) (2) (3) (8) (4) (7) (6) (5)

- 4±0.2

- 5±0.2

- 2±0.2

- 2±0.1 0.3±0.2 0.1±0.1

- 0±0.1