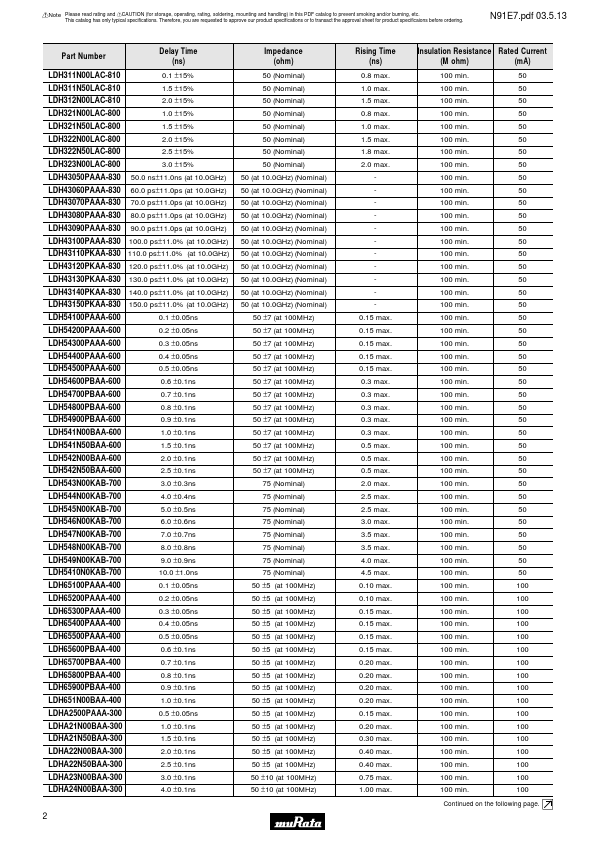

LDH541N50BAA-600 Description

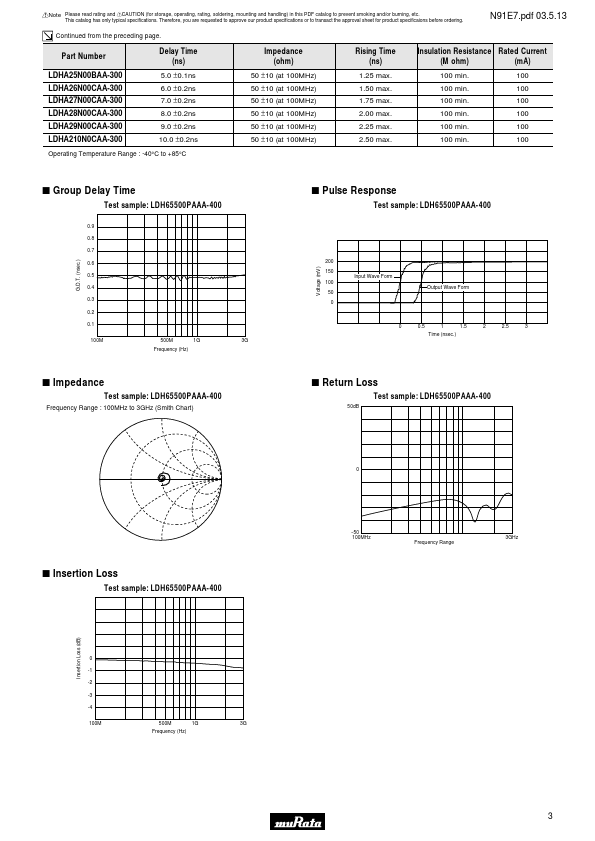

!Note PPleleaasseerreeaaddrraatitninggaanndd!!CCAAUUTTIOIONN((foforrsstotorraaggee,,ooppeerraatitningg,,rraatitningg,,ssooldldeerriningg,,mmoouunntitninggaannddhhaannddlilningg))ininththisisPcDatFalcoagtatolopgrteovepnretvsemnot ksimngokaindg/oarndb/uorrnbinugr,neintgc., etc. N91E7.pdf 03.5.13 TThhisisccaatatalologghhaassoonnlylytytyppiciacal sl...