MTV112M

MTV112M is 8051 Embedded CRT Monitor Controller Flash Version manufactured by Myson.

FEATURES l l l l l l l l l l l l l l

8051 core. 384-bytes internal RAM. 32K-bytes program Flash ROM. 14-channels 5V open-drain PWM DAC, 10 dedicated channels and 4 channels shared with I/O pin. 28 bi-direction I/O pin,12 dedicated pin,12 shared with DAC, 4 shared with DDC/IIC interface. 3-output pin shared with H/V sync output and self test output pins. SYNC processor for posite separation, polarity and frequency check, and polarity adjustment. Built-in monitor self-test pattern generator. Built-in low power reset circuit. One slave mode IIC interface and one master mode IIC interface. IIC interface for DDC1/DDC2B and EEPROM, only one EEPROM needed to store DDC1/DDC2B and display mode information. Dual 4-bit ADC or 4 channel 6-bit ADC. Watchdog timer with programmable interval. 40-pin PDIP and 44-pin PLCC package.

GENERAL DESCRIPTION

The MTV112M micro-controller is an 8051 CPU core embedded device specially tailored to CRT monitor applications. It includes an 8051 CPU core, 384-byte SRAM, 14 built-in PWM DACs, DDC1/DDC2B interface, 24Cxx series EEPROM interface, A/D converter and a 32K bytes internal program Flash ROM.

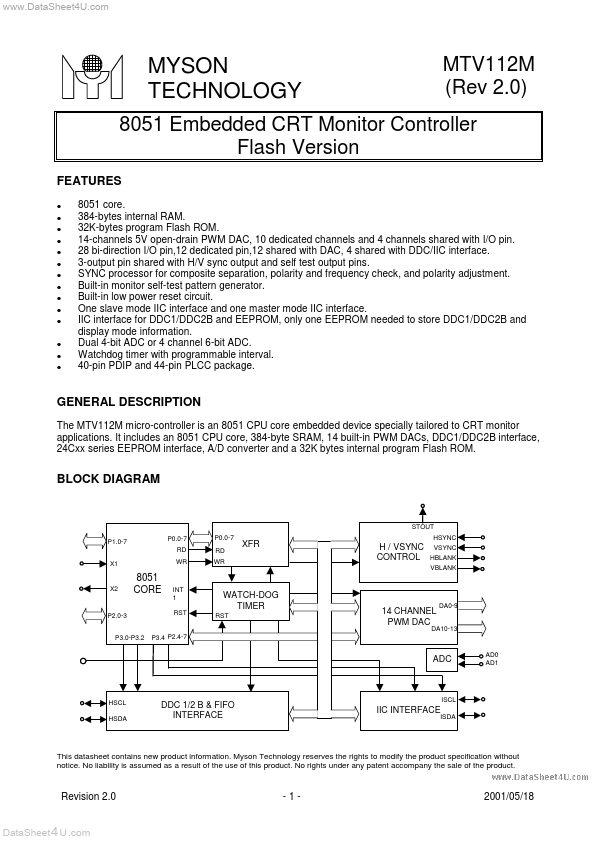

BLOCK DIAGRAM

STOUT P1.0-7 X1 P0.0-7 RD WR P0.0-7 RD WR

HSYNC

H / VSYNC CONTROL

VSYNC HBLANK VBLANK

X2

8051 CORE

INT 1 RST

WATCH-DOG TIMER

P2.0-3 P3.0-P3.2

14 CHANNEL PWM DAC

DA0-9

DA10-13

P3.4 P2.4-7

AD0 AD1

HSCL HSDA

DDC 1/2 B & FIFO INTERFACE

ISCL

IIC INTERFACE

ISDA

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent acpany the sale of the product.

Revision 2.0

-1-

2001/05/18

Data Sheet 4 U .

..

MYSON TECHNOLOGY

1.0 PIN CONNECTION

MTV112M (Rev 2.0)

P1.0 P1.1/HALFV P1.2/HALFH P1.3/HCLAMP P1.4/AD2 P1.5/AD3 P1.6/AD0 P1.7/AD1 RST HSCL/P3.0/Rxd HSDA/P3.1/Txd ISDA/P3.2/INT0 HSYNC ISCL/P3.4/T0 VSYNC HBLANK/P4.1 VBLANK/P4.0 X2 X1...