UPD23C64202L

Description

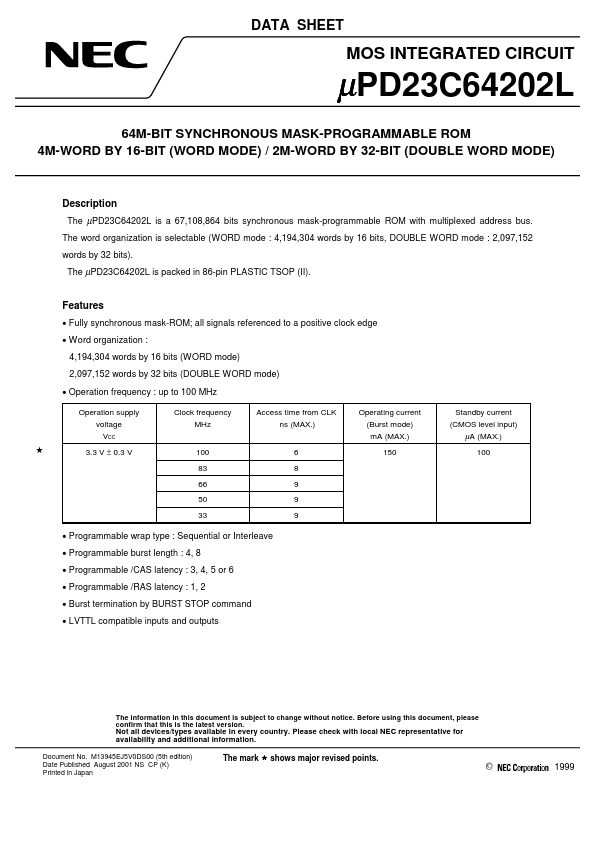

The µPD23C64202L is a 67,108,864 bits synchronous mask-programmable ROM with multiplexed address bus. The word organization is selectable (WORD mode : 4,194,304 words by 16 bits, DOUBLE WORD mode : 2,097,152 words by 32 bits). The µPD23C64202L is packed in 86-pin PLASTIC TSOP (II).

Features

- Fully synchronous mask-ROM; all signals referenced to a positive clock edge

- Word organization : 4,194,304 words by 16 bits (WORD mode) 2,097,152 words by 32 bits (DOUBLE WORD mode)

- Operation frequency : up to 100 MHz

Operation supply voltage VCC Clock frequency MHz Access time from CLK ns (MAX.) Operating current (Burst mode) m A (MAX.) 150 Standby current (CMOS level input) µA (MAX.) 100

3.3 V ± 0.3 V

100 83 66 50 33

6 8 9 9 9

- Programmable wrap type : Sequential or Interleave

- Programmable burst length : 4, 8

- Programmable /CAS latency : 3, 4, 5 or 6

- Programmable /RAS latency : 1, 2

- Burst termination by BURST STOP mand

- LVTTL patible inputs and outputs

The...