D45128441G5

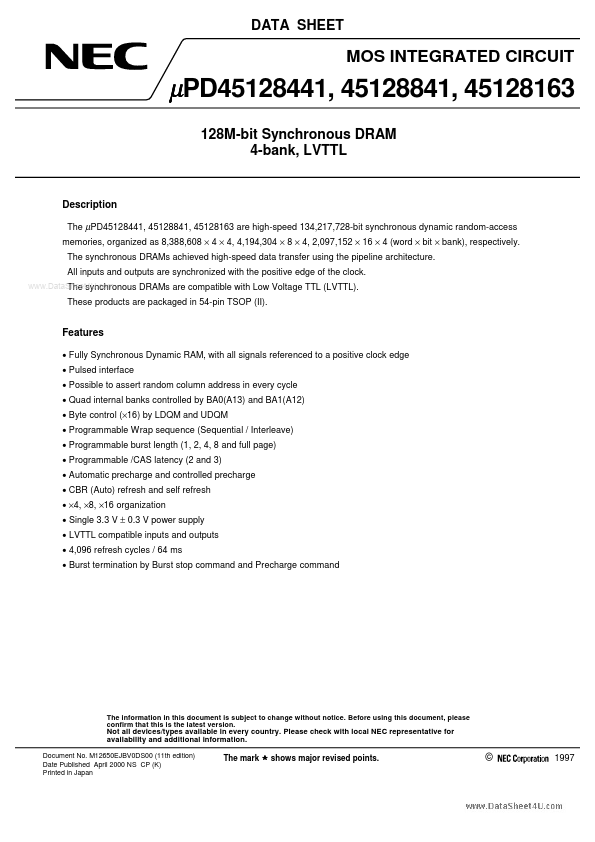

Description

The µPD45128441, 45128841, 45128163 are high-speed 134,217,728-bit synchronous dynamic random-access memories, organized as 8,388,608 × 4 × 4, 4,194,304 × 8 × 4, 2,097,152 × 16 × 4 (word × bit × bank), respectively. The synchronous DRAMs achieved high-speed data transfer using the pipeline architecture.

Key Features

- Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

- Pulsed interface

- Possible to assert random column address in every cycle

- Quad internal banks controlled by BA0(A13) and BA1(A12)

- Byte control (×16) by LDQM and UDQM

- Programmable Wrap sequence (Sequential / Interleave)

- Programmable burst length (1, 2, 4, 8 and full page)

- Programmable /CAS latency (2 and 3)

- Automatic precharge and controlled precharge

- CBR (Auto) refresh and self refresh