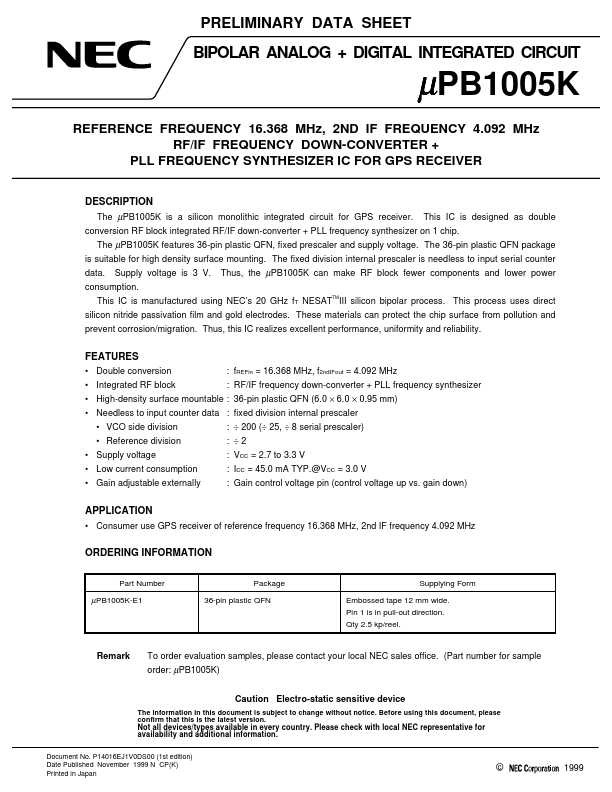

UPB1005K

DESCRIPTION

The µPB1005K is a silicon monolithic integrated circuit for GPS receiver. This IC is designed as double conversion RF block integrated RF/IF down-converter + PLL frequency synthesizer on 1 chip. The µPB1005K features

36-pin plastic QFN, fixed prescaler and supply voltage. The 36-pin plastic QFN package is suitable for high density surface mounting. The fixed division internal prescaler is needless to input serial counter data. Supply voltage is 3 V. Thus, the µPB1005K can make RF block fewer ponents and lower power consumption. This IC is manufactured using NEC’s 20 GHz f T NESATTMIII silicon bipolar process. This process uses direct silicon nitride passivation film and gold electrodes. These materials can protect the chip surface from pollution and prevent corrosion/migration. Thus, this IC realizes excellent performance, uniformity and reliability.

FEATURES

- Double conversion

- Integrated RF block : f REFin = 16.368 MHz, f2nd IFout = 4.092 MHz : RF/IF frequency...