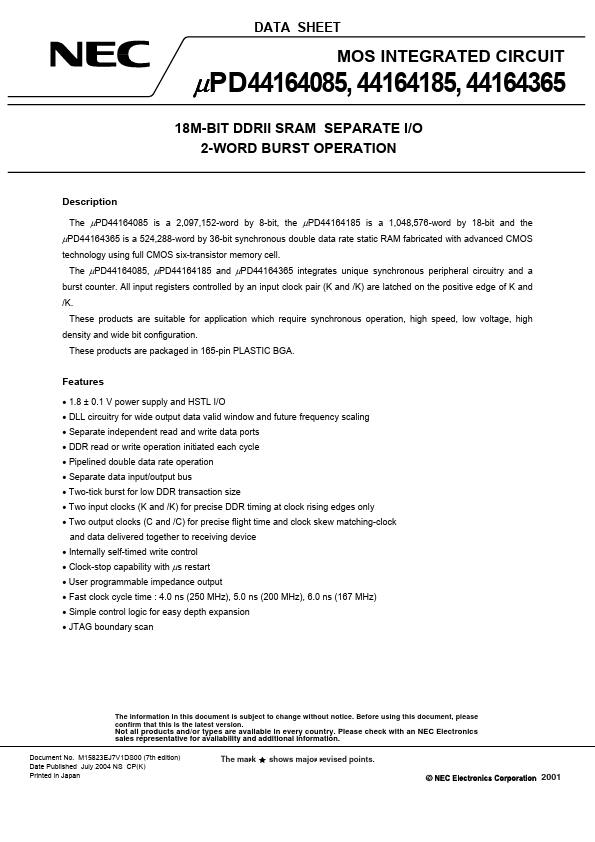

UPD44164085

Description

The µPD44164085 is a 2,097,152-word by 8-bit, the µPD44164185 is a 1,048,576-word by 18-bit and the

µPD44164365 is a 524,288-word by 36-bit synchronous double data rate static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell. The µPD44164085, µPD44164185 and µPD44164365 integrates unique synchronous peripheral circuitry and a burst counter. All input registers controlled by an input clock pair (K and /K) are latched on the positive edge of K and /K. These products are suitable for application which require synchronous operation, high speed, low voltage, high density and wide bit configuration. These products are packaged in 165-pin PLASTIC BGA.

Features

- 1.8 ± 0.1 V power supply and HSTL I/O

- DLL circuitry for wide output data valid window and future frequency scaling

- Separate independent read and write data ports

- DDR read or write operation initiated each cycle

- Pipelined double data rate operation

- Separate data...