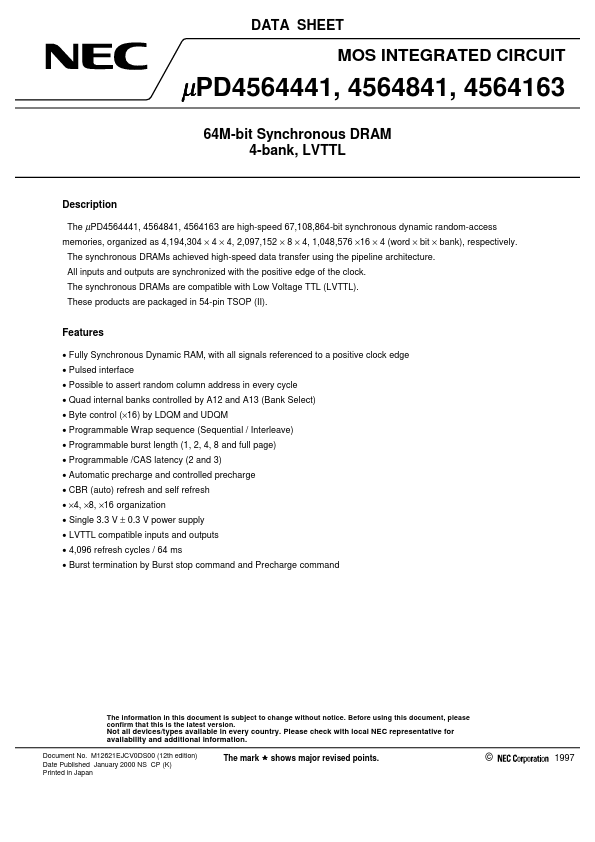

UPD4564163

Description

The µPD4564441, 4564841, 4564163 are high-speed 67,108,864-bit synchronous dynamic random-access memories, organized as 4,194,304 × 4 × 4, 2,097,152 × 8 × 4, 1,048,576 ×16 × 4 (word × bit × bank), respectively.

The synchronous DRAMs achieved high-speed data transfer using the pipeline architecture. All inputs and outputs are synchronized with the positive edge of the clock. The synchronous DRAMs are patible with Low Voltage TTL (LVTTL). These products are packaged in 54-pin TSOP (II).

Features

- Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

- Pulsed interface

- Possible to assert random column address in every cycle

- Quad internal banks controlled by A12 and A13 (Bank Select)

- Byte control (×16) by LDQM and UDQM

- Programmable Wrap sequence (Sequential / Interleave)

- Programmable burst length (1, 2, 4, 8 and full page)

- Programmable /CAS latency (2 and 3)

- Automatic precharge and controlled precharge

- CBR (auto) refresh and self...