Datasheet Summary

DATA SHEET

MOS INTEGRATED CIRCUIT

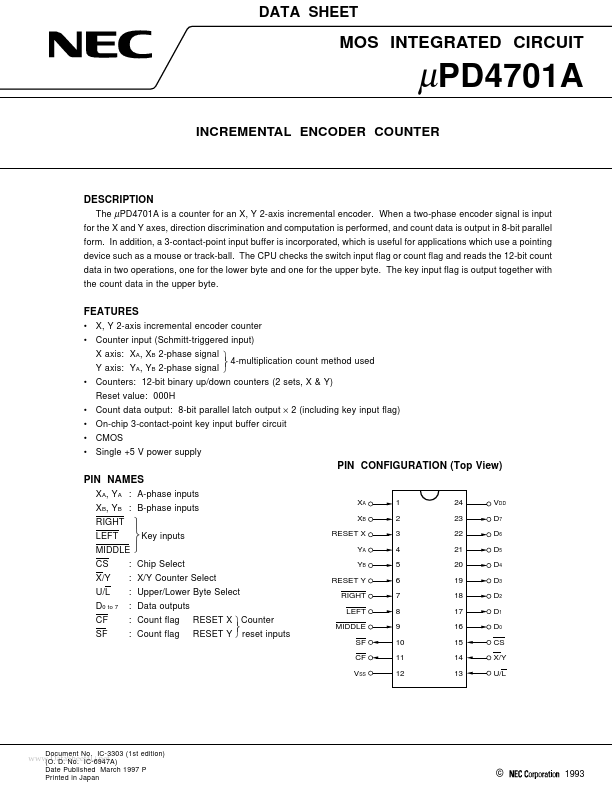

µPD4701A

INCREMENTAL ENCODER COUNTER

DESCRIPTION

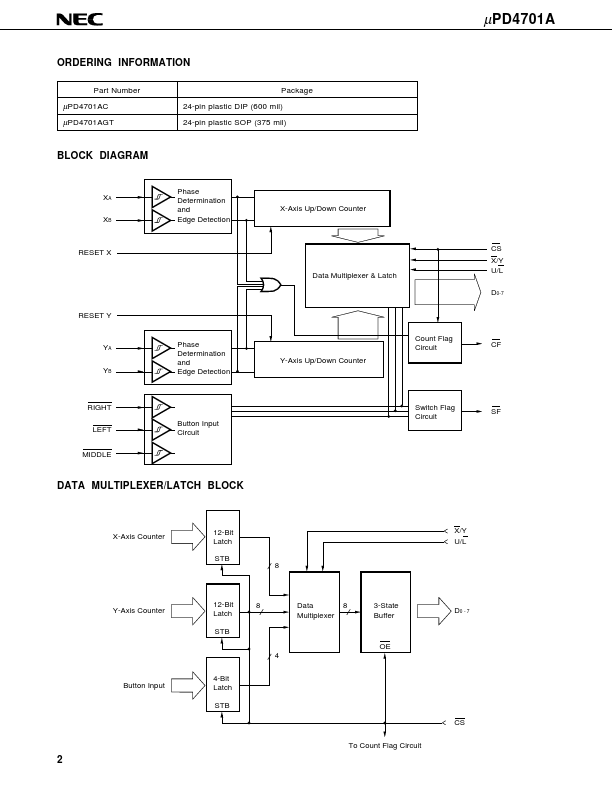

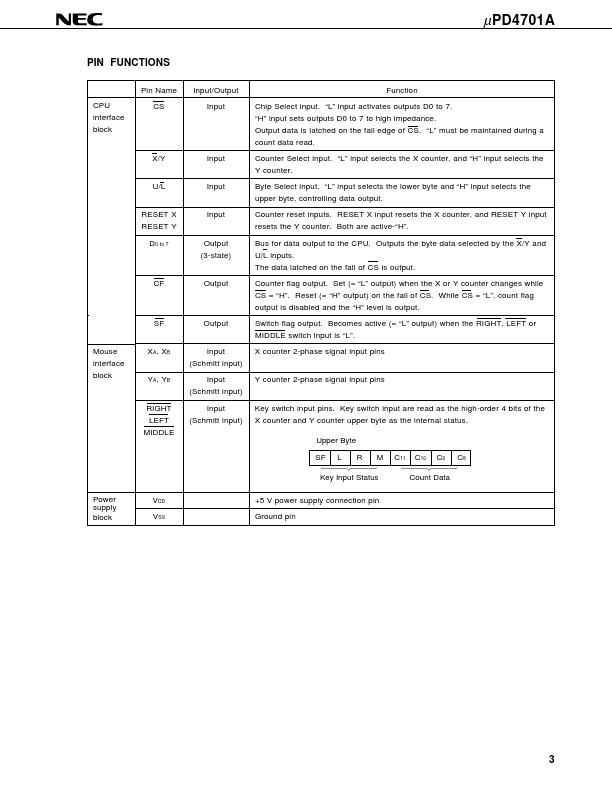

The µPD4701A is a counter for an X, Y 2-axis incremental encoder. When a two-phase encoder signal is input for the X and Y axes, direction discrimination and putation is performed, and count data is output in 8-bit parallel form. In addition, a 3-contact-point input buffer is incorporated, which is useful for applications which use a pointing device such as a mouse or track-ball. The CPU checks the switch input flag or count flag and reads the 12-bit count data in two operations, one for the lower byte and one for the upper byte. The key input flag is output together with the count data in the upper...