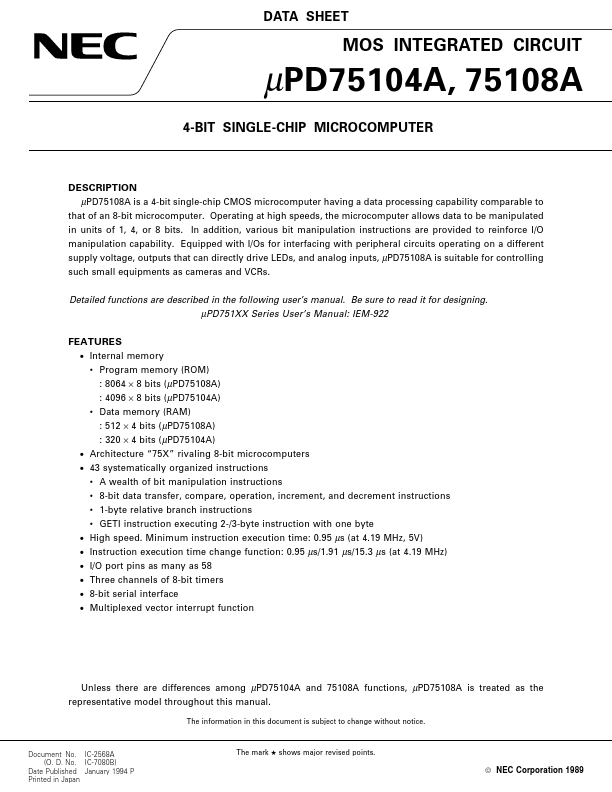

UPD75104A

Description

µPD75108A is a 4-bit single-chip CMOS microcomputer having a data processing capability comparable to that of an 8-bit microcomputer. Operating at high speeds, the microcomputer allows data to be manipulated in units of 1, 4, or 8 bits.

Key Features

- Internal memory

- Program memory (ROM) : 8064 × 8 bits (µ PD75108A) : 4096 × 8 bits (µ PD75104A)

- Data memory (RAM) : 512 × 4 bits ( µPD75108A) : 320 × 4 bits ( µPD75104A)

- Architecture “75X” rivaling 8-bit microcomputers

- 43 systematically organized instructions

- A wealth of bit manipulation instructions

- 8-bit data transfer, compare, operation, increment, and decrement instructions

- 1-byte relative branch instructions

- GETI instruction executing 2-/3-byte instruction with one byte

- High speed. Minimum instruction execution time: 0.95 µs (at 4.19 MHz, 5V)