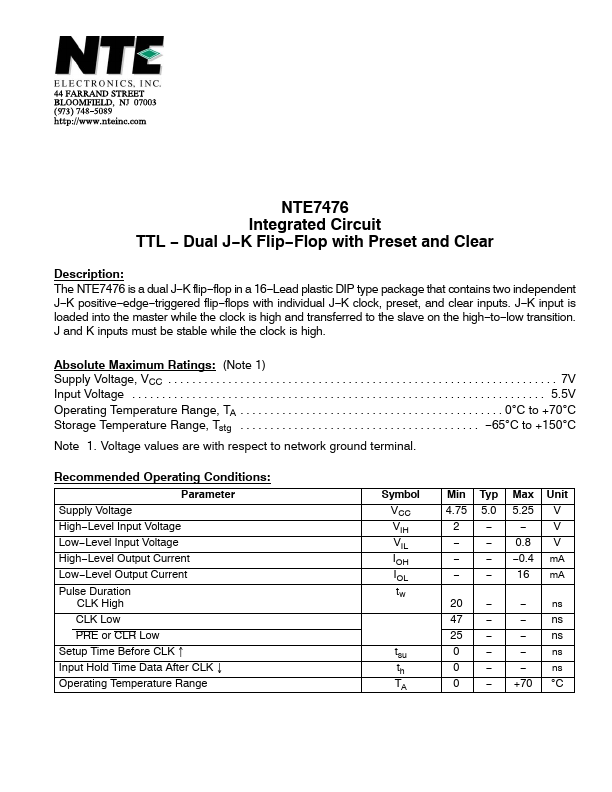

7476

Overview

The NTE7476 is a dual J-K flip-flop in a 16-Lead plastic DIP type package that contains two independent J-K positive-edge-triggered flip-flops with individual J-K clock, preset, and clear inputs. J-K input is loaded into the master while the clock is high and transferred to the slave on the high-to-low transition.