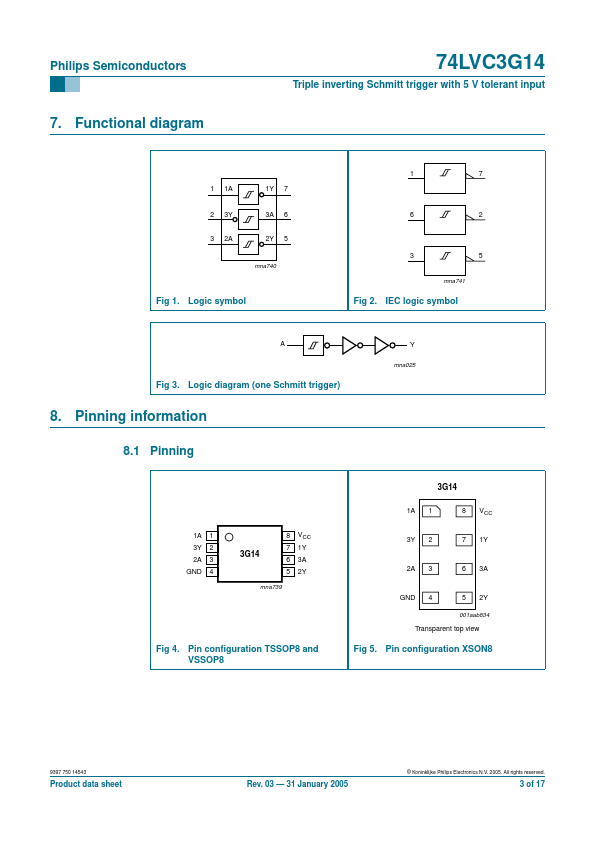

Datasheet Summary

Triple inverting Schmitt trigger with 5 V tolerant input

Rev. 03

- 31 January 2005 Product data sheet

1. General description

The 74LVC3G14 is a high-performance, low-power, low-voltage, Si-gate CMOS device and superior to most advanced CMOS patible TTL-families. Inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of this device as translator in a mixed 3.3 V and 5 V environment. This device is fully specified for partial power-down applications using Ioff. The Ioff circuitry disables the output, preventing the damaging backflow current through the device when it is powered down. The 74LVC3G14 provides three inverting buffers with Schmitt-trigger...