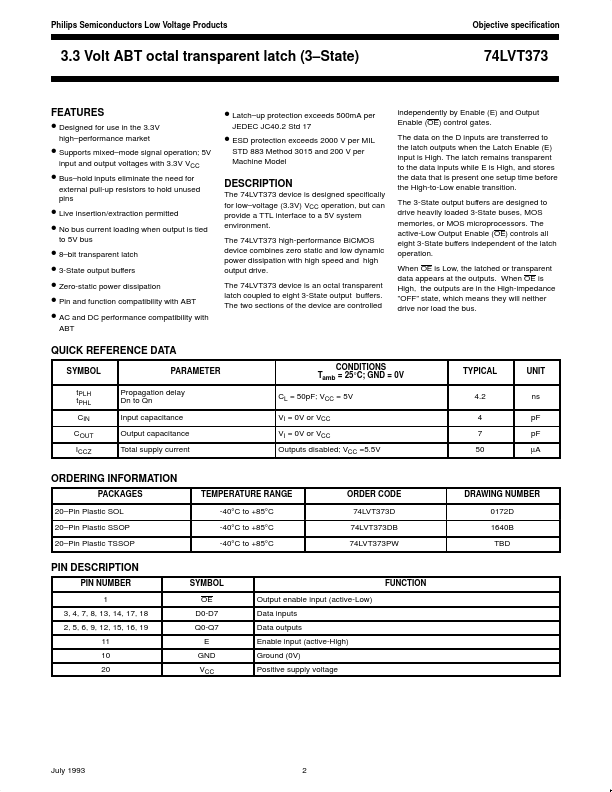

74LVT373

FEATURES

- Designed for use in the 3.3V high- performance market

- Latch- up protection exceeds 500m A per

JEDEC JC40.2 Std 17 independently by Enable (E) and Output Enable (OE) control gates. The data on the D inputs are transferred to the latch outputs when the Latch Enable (E) input is High. The latch remains transparent to the data inputs while E is High, and stores the data that is present one setup time before the High-to-Low enable transition. The 3-State output buffers are designed to drive heavily loaded 3-State buses, MOS memories, or MOS microprocessors. The active-Low Output Enable (OE) controls all eight 3-State buffers independent of the latch operation. When OE is Low, the latched or transparent data appears at the outputs. When OE is High, the outputs are in the High-impedance ”OFF” state, which means they will neither drive nor load the bus.

- Supports mixed- mode signal operation; 5V

- Bus- hold inputs eliminate the need for input and output voltages with 3.3V VCC...