MC33910 Overview

Key Specifications

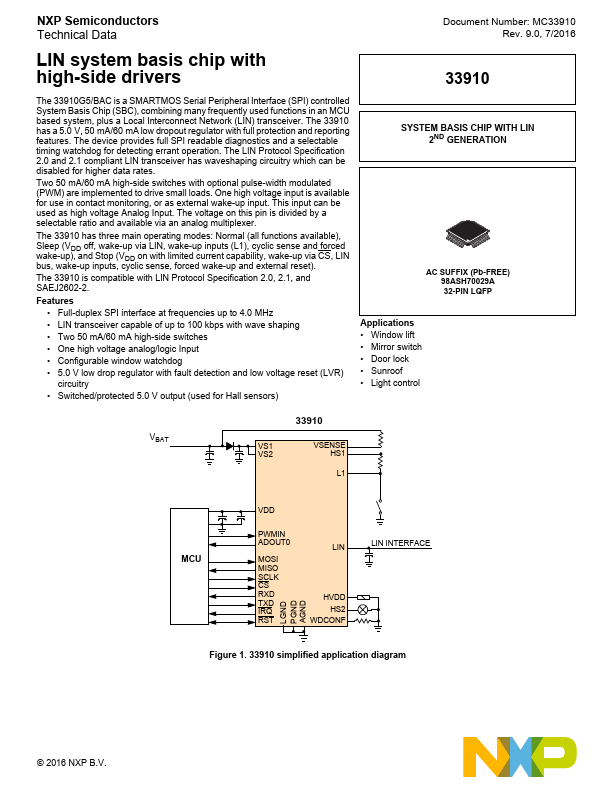

Package: LQFP

Mount Type: Surface Mount

Pins: 32

Operating Voltage: 13.5 V

Key Features

- Full-duplex SPI interface at frequencies up to 4.0 MHz

- LIN transceiver capable of up to 100 kbps with wave shaping

- Two 50 mA/60 mA high-side switches

- One high voltage analog/logic Input

- Configurable window watchdog