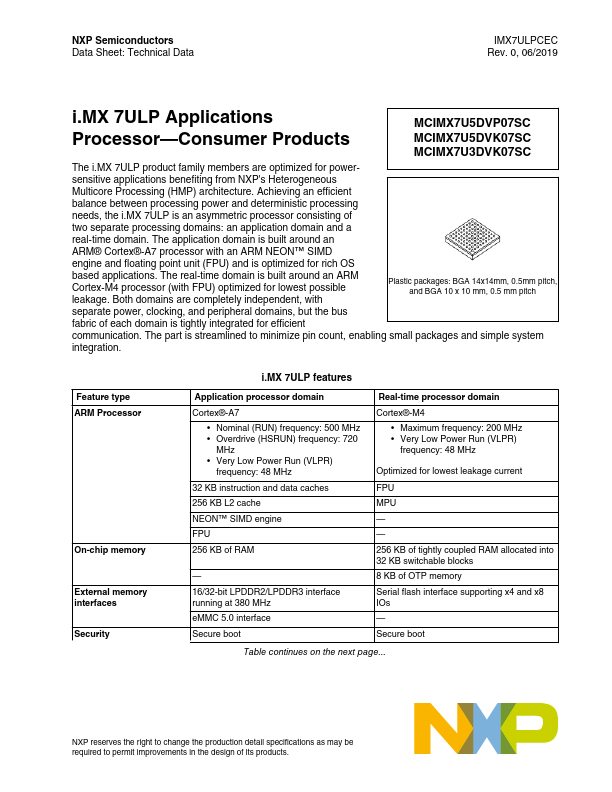

| Part | MCIMX7U5DVP07SC |

|---|---|

| Description | Applications Processor |

| Manufacturer | NXP Semiconductors |

| Size | 2.22 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| RK3588 | Rockchip | high performance processor |

| BP1048B2 | MVSILICON | High-performance 32-bit Bluetooth audio application processor |

| RK3576 | Rockchip | high performance processor |