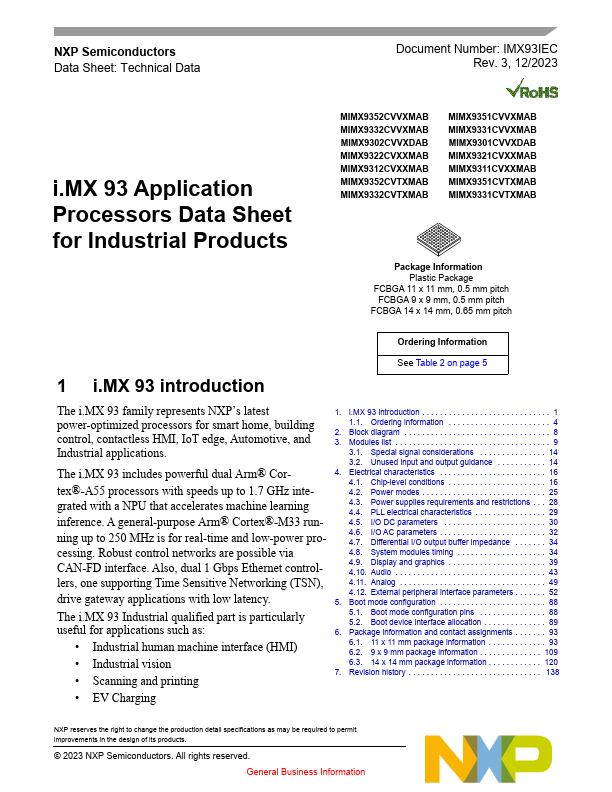

| Part | MIMX9352CVVXMAB |

|---|---|

| Description | i.MX 93 Application Processors |

| Manufacturer | NXP Semiconductors |

| Size | 2.58 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| i.MX28 | NXP Semiconductors | Applications Processors |

| I.MX31 | Freescale Semiconductor | Multimedia Applications Processors |

| i.MX35 | Freescale Semiconductor | Applications Processors |