MPC5510

MPC5510 is Microcontroller manufactured by NXP Semiconductors.

NXP Semiconductors Data Sheet: Technical Data

Document Number: MPC5510 Rev. 5, 7/2019

MPC5510 Microcontroller Family Data Sheet

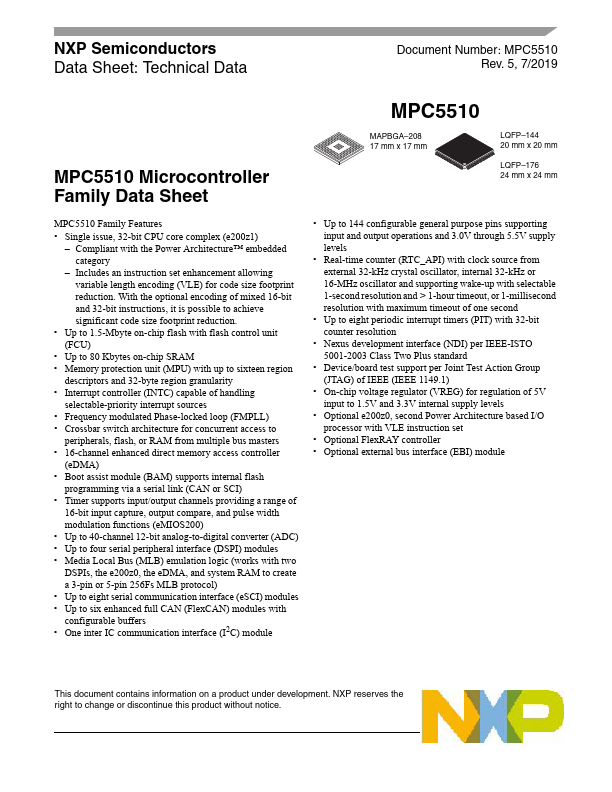

MMAAPPBBGGAA-

- 220285 1175mmmmxx1175mmmm

QFNL1Q2 FP- 144 ##_m2m0 _mxm_#x#m20mmm

SOT-343R ##_mm_x_##mm

LQFP- 176 PKG2-4TBmDm x 24 mm ## mm x ## mm

MPC5510 Family Features

- Single issue, 32-bit CPU core plex (e200z1)

- pliant with the Power Architecture™ embedded category

- Includes an instruction set enhancement allowing variable length encoding (VLE) for code size footprint reduction. With the optional encoding of mixed 16-bit and 32-bit instructions, it is possible to achieve significant code size footprint reduction.

- Up to 1.5-Mbyte...