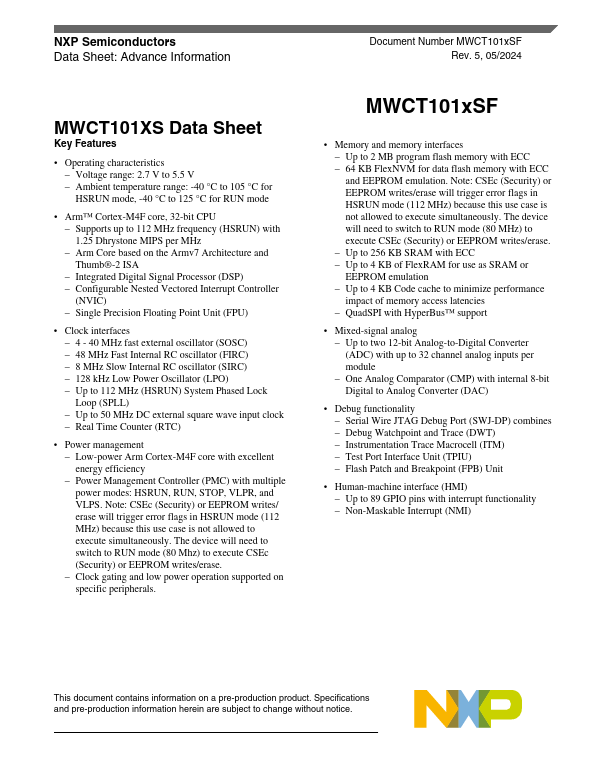

MWCT1016S

MWCT1016S is 32-bit CPU manufactured by NXP Semiconductors.

- Part of the MWCT101XSF comparator family.

- Part of the MWCT101XSF comparator family.

Features

- Operating characteristics

- Voltage range: 2.7 V to 5.5 V

- Ambient temperature range: -40 °C to 105 °C for HSRUN mode, -40 °C to 125 °C for RUN mode

- Arm™ Cortex-M4F core, 32-bit CPU

- Supports up to 112 MHz frequency (HSRUN) with 1.25 Dhrystone MIPS per MHz

- Arm Core based on the Armv7 Architecture and Thumb®-2 ISA

- Integrated Digital Signal Processor (DSP)

- Configurable Nested Vectored Interrupt Controller (NVIC)

- Single Precision Floating Point Unit (FPU)

- Clock interfaces

- 4

- 40 MHz fast external oscillator (SOSC)

- 48 MHz Fast Internal RC oscillator (FIRC)

- 8 MHz Slow Internal RC oscillator (SIRC)

- 128 k Hz Low Power Oscillator (LPO)

- Up to 112 MHz (HSRUN) System Phased Lock Loop (SPLL)

- Up to 50 MHz DC external square wave input clock

- Real Time Counter (RTC)

- Power management

- Low-power Arm Cortex-M4F core with excellent energy efficiency

- Power Management Controller (PMC) with multiple power modes: HSRUN, RUN, STOP, VLPR, and VLPS. Note: CSEc (Security) or EEPROM writes/ erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. The device will need to switch to RUN mode (80 Mhz) to execute CSEc (Security) or EEPROM writes/erase.

- Clock gating and low power operation supported on specific peripherals.

Document Number MWCT101x SF Rev. 5, 05/2024

MWCT101x SF

- Memory and memory interfaces

- Up to 2 MB program flash memory with ECC

- 64 KB Flex NVM for data flash memory with ECC and EEPROM emulation. Note: CSEc (Security) or EEPROM writes/erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. The device will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.

- Up to 256 KB SRAM with ECC

- Up to 4 KB of Flex RAM for use as SRAM or EEPROM emulation

- Up to 4 KB Code cache to minimize performance impact of memory access latencies

- Quad SPI with Hyper Bus™ support

- Mixed-signal...