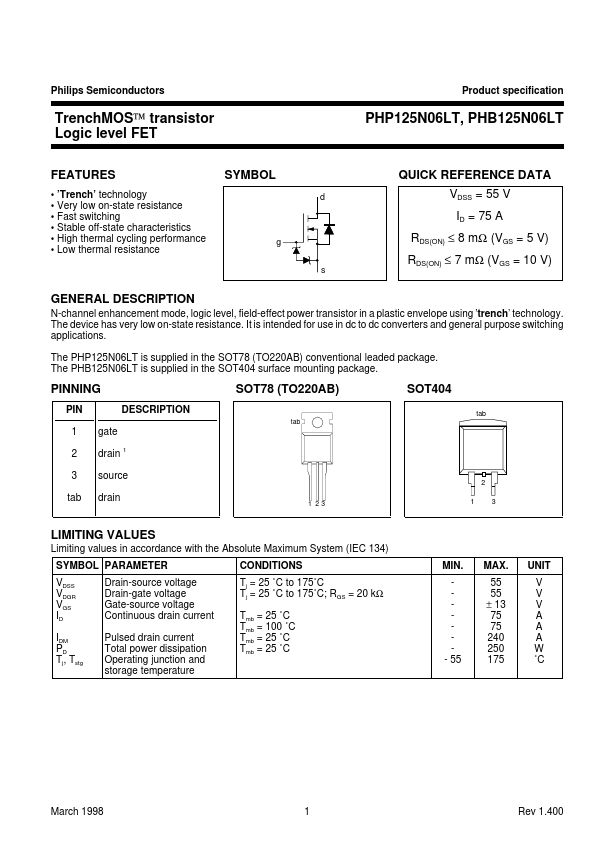

PHP125N06LT Overview

Description

N-channel enhancement mode, logic level, field-effect power transistor in a plastic envelope using ’trench’ technology. The device has very low on-state resistance.

Key Features

- Very low on-state resistance

- Fast switching

- Stable off-state characteristics

- High thermal cycling performance