PHX5N50E Overview

Description

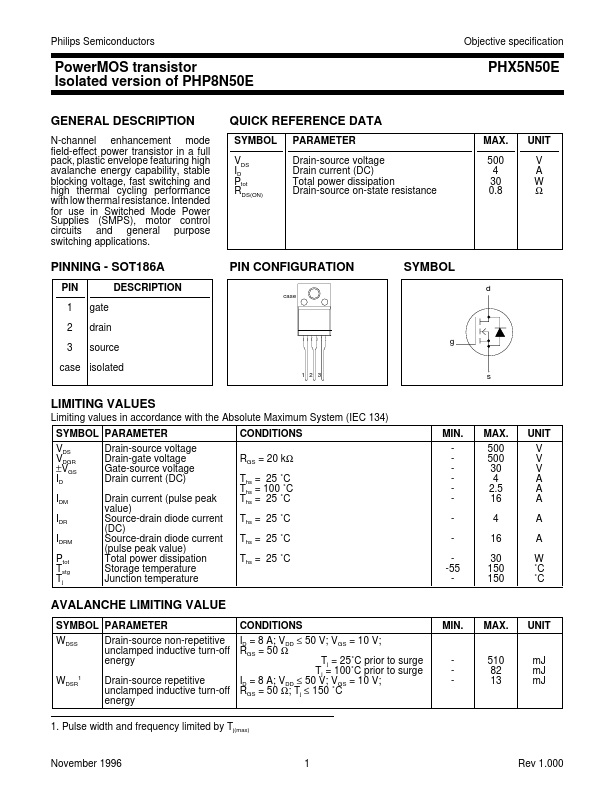

N-channel enhancement mode field-effect power transistor in a full pack, plastic envelope featuring high avalanche energy capability, stable blocking voltage, fast switching and high thermal cycling performance with low PHX5N50E QUICK REFERENCE DATA SYMBOL VDS ID Ptot RDS(ON) PARAMETER Drain-source voltage Drain current (DC) Total power dissipation Drain-source on-state resistance MAX. 500 4 30 0.8 UNIT V A W Ω PINNING - SOT186A PIN 1 2 3 gate drain source DESCRIPTION.