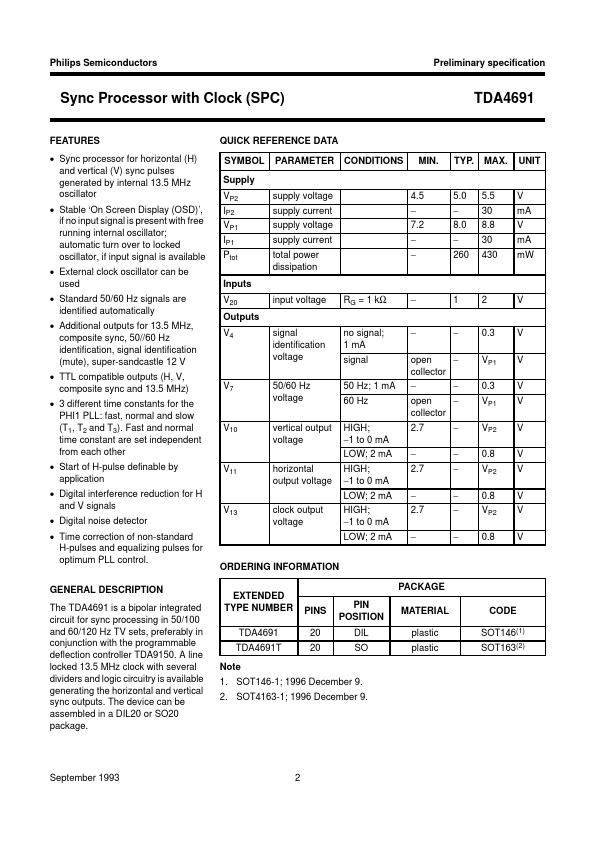

TDA4691 Overview

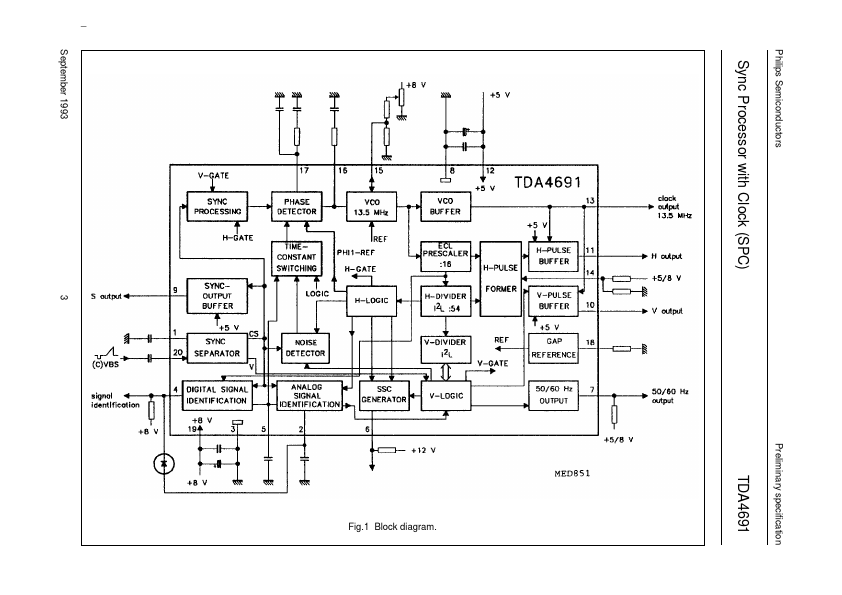

The TDA4691 is a bipolar integrated circuit for sync processing in 50/100 and 60/120 Hz TV sets, preferably in conjunction with the programmable deflection controller TDA9150. A line locked 13.5 MHz clock with several dividers and logic circuitry is available generating the horizontal and vertical sync outputs. The device can be assembled in a DIL20 or SO20 package.

TDA4691 Key Features

- Sync processor for horizontal (H) and vertical (V) sync pulses generated by internal 13.5 MHz oscillator

- Stable ‘On Screen Display (OSD)’, if no input signal is present with free running internal oscillator; automatic turn ov

- External clock oscillator can be used

- Standard 50/60 Hz signals are identified automatically

- Additional outputs for 13.5 MHz, posite sync, 50//60 Hz identification, signal identification (mute), super-sandcastle 1

- TTL patible outputs (H, V, posite sync and 13.5 MHz)

- 3 different time constants for the PHI1 PLL: fast, normal and slow (T1, T2 and T3). Fast and normal time constant are se

- Start of H-pulse definable by application

- Digital interference reduction for H and V signals

- Digital noise detector