NT5DS4M32EG

NT5DS4M32EG is 1M X 32 Bits X 4 Banks Double Data Rate Synchronous RAM manufactured by NanoAmp Solutions.

Overview

The NT5DS4M32EG is 134,217,728 bits of double data rate synchronous dynamic RAM organized as 4 x 1,048,576 bits by 32 I/Os. Synchronous features with Data Strobe allow extremely high performance up to 400Mbps/pin. I/O transactions are possible on both edges of the clock. Range of operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications.

Features

- VDD = 2.5V±5% , VDDQ = 2.5V±5%

- SSTL_2 patible inputs/outputs

- 4 banks operation

- MRS cycle with address key programs

- Data I/O transaction on both edges of Data strobe

- 4 DQS (1 DQS/Byte)

- DLL aligns DQ and DQS transaction with Clock transaction

- Edge aligned data & data strobe output

- Center aligned data & data strobe input

- DM for write masking only

- Auto & self refresh

- 32ms refresh period (4K cycle)

- 144-Ball FBGA package

- Maximum clock frequency up to 200MHz

- Maximum data rate up to 400Mbps/pin

-CAS latency 2,3 (clock) -Burst length (2, 4, 8 and Full page) -Burst type (sequential & interleave)

- Full page burst length for sequential burst type only

- Start address of the full page burst should be even

- All inputs except data & DM are sampled at the rising edge of the system clock

- Differential clock input(CK & /CK)

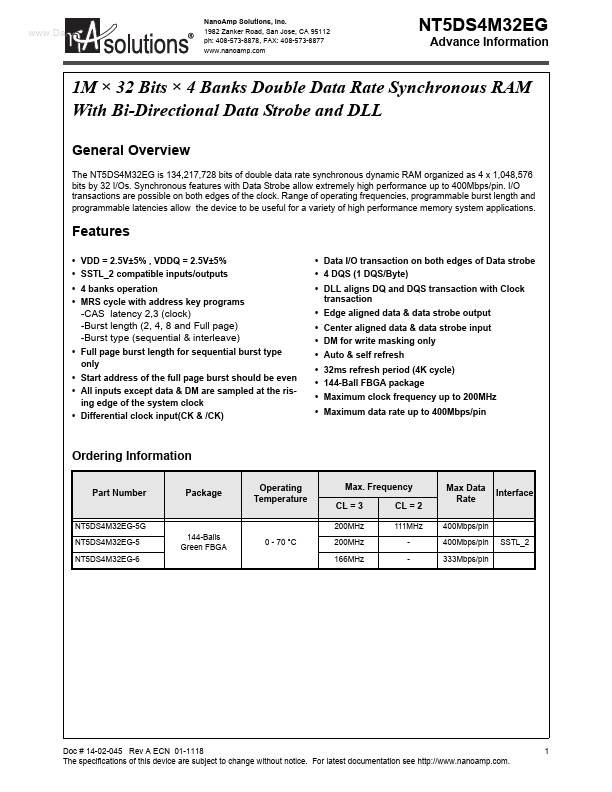

Ordering Information

Part Number Package Operating Temperature Max. Frequency CL = 3

200MHz 144-Balls Green FBGA 0

- 70 °C 200MHz 166MHz

CL = 2

111MHz

- Max Data Rate

400Mbps/pin 400Mbps/pin 333Mbps/pin

Interface

NT5DS4M32EG-5G NT5DS4M32EG-5 NT5DS4M32EG-6

SSTL_2

Doc # 14-02-045 Rev A ECN 01-1118 The specifications of this device are subject to change without notice. For latest documentation see http://.nanoamp..

Nano Amp Solutions, Inc. Figure 1: PIN CONFIGURATION (Top View)

Advance Information

1 A B C D E F G H J K L M

DQS0 DQ4 DQ6 DQ7 DQ17 DQ19 DQS2 DQ21 DQ22 /CAS /RAS...