NT5SV64M4AT Overview

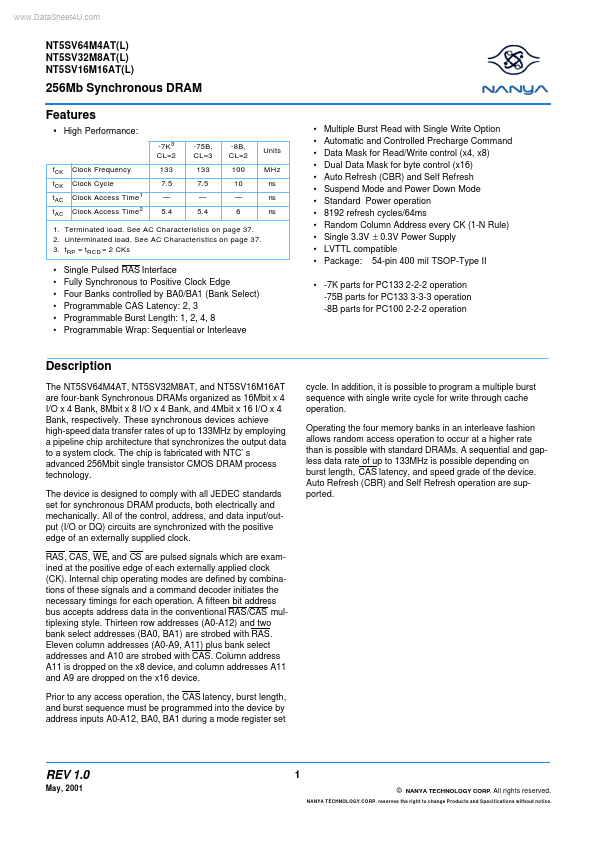

Key Specifications

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 3 V

Max Frequency: 133 MHz

Description

The NT5SV64M4AT, NT5SV32M8AT, and NT5SV16M16AT are four-bank Synchronous DRAMs organized as 16Mbit x 4 I/O x 4 Bank, 8Mbit x 8 I/O x 4 Bank, and 4Mbit x 16 I/O x 4 Bank, respectively. These synchronous devices achieve high-speed data transfer rates of up to 133MHz by employing a pipeline chip architecture that synchronizes the output data to a system clock.

Key Features

- High Performance

- Terminated load. See AC Characteristics on page

- 2. Unterminated load. See AC Characteristics on page

- 3. tRP = tRCD = 2 CKs