54AC161 Overview

Key Specifications

Package: CDIP

Mount Type: Through Hole

Pins: 16

Max Voltage (typical range): 5.5 V

Description

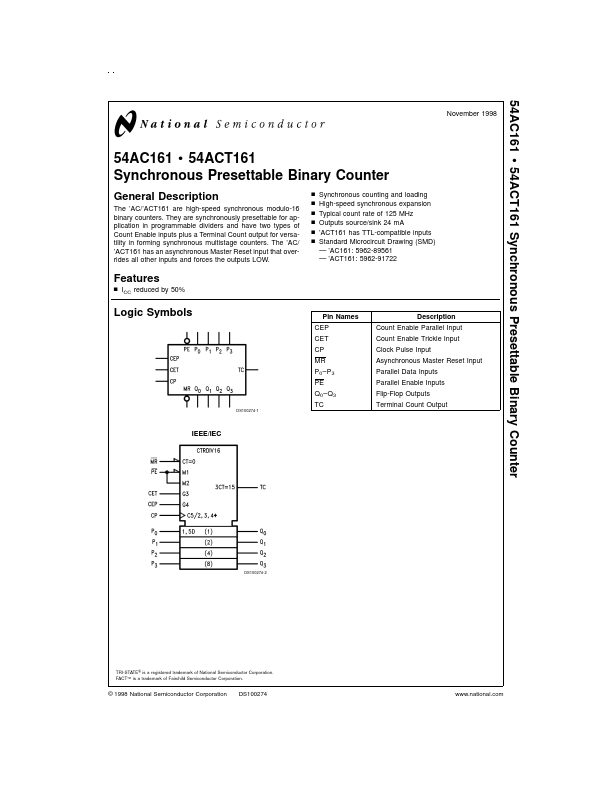

The ’AC/’ACT161 are high-speed synchronous modulo-16 binary counters. They are synchronously presettable for application in programmable dividers and have two types of Count Enable inputs plus a Terminal Count output for versatility in forming synchronous multistage counters.

Key Features

- n ICC reduced by 50% Logic Symbols Pin Names CEP CET CP MR P0–P3 PE Q0–Q3 TC DS100274-1