54ACTQ10

54ACTQ10 is Quiet Series Triple 3-Input NAND Gate manufactured by National Semiconductor.

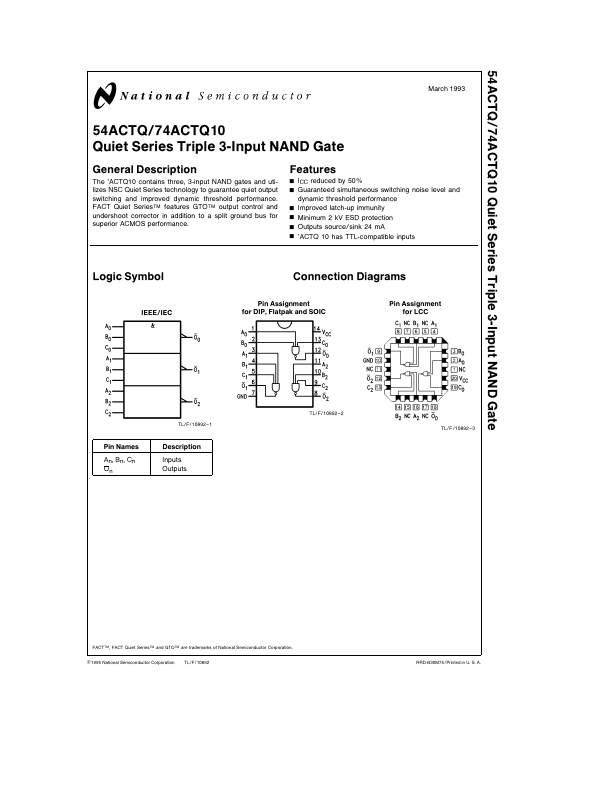

54ACTQ 74ACTQ10 Quiet Series Triple 3-Input NAND Gate

March 1993

54ACTQ 74ACTQ10 Quiet Series Triple 3-Input NAND Gate

General Description

The ’ACTQ10 contains three 3-input NAND gates and utilizes NSC Quiet Series technology to guarantee quiet output switching and improved dynamic threshold performance FACT Quiet SeriesTM Features

GTOTM output control and undershoot corrector in addition to a split ground bus for superior ACMOS performance

Features

Y ICC reduced by 50% Y Guaranteed simultaneous switching noise level and dynamic threshold performance Y Improved latch-up immunity Y Minimum 2 kV ESD protection Y Outputs source sink 24 mA Y ’ACTQ 10 has TTL-patible inputs

Logic...