54ACTQ374

54ACTQ374 is Quiet Series Octal D Flip-Flop manufactured by National Semiconductor.

- Part of the 54ACQ374 comparator family.

- Part of the 54ACQ374 comparator family.

Description

The ’ACQ/’ACTQ374 is a high-speed, low-power octal D-type flip-flop featuring separate D-type inputs for each flip-flop and TRI-STATE outputs for bus-oriented applications. A buffered Clock (CP) and Output Enable (OE) are mon to all flip-flops. The ’ACQ/’ACTQ374 utilizes Quiet Series technology to guarantee quiet output switching and improve dynamic threshold performance. FACT Quiet Series™ features

GTO™ output control and undershoot corrector in addition to a split ground bus for superior performance. n Guaranteed simultaneous switching noise level and dynamic threshold performance n Improved latch-up immunity n Buffered positive edge-triggered clock n TRI-STATE outputs drive bus lines or buffer memory address registers n Outputs source/sink 24 m A n Faster prop delays than the standard ’AC/’ACT374 n 4 k V minimum ESD immunity n Standard Military Drawing (SMD)

- ’ACTQ374: 5962-92189

- ’ACQ374: 5962-92179

Features n ICC and IOZ reduced by 50%

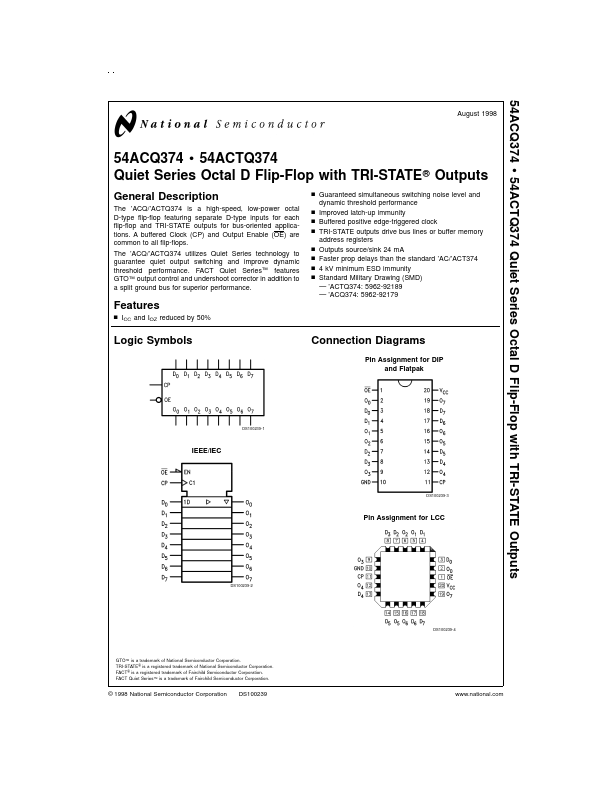

Logic Symbols

Connection Diagrams

Pin Assignment for DIP and Flatpak

DS100239-1

IEEE/IEC

DS100239-3

Pin Assignment for LCC

DS100239-2

DS100239-4

GTO™ is a trademark of National Semiconductor Corporation. TRI-STATE ® is a registered trademark of National Semiconductor Corporation. FACT ® is a registered trademark of Fairchild Semiconductor Corporation. FACT Quiet Series™ is a trademark of Fairchild Semiconductor Corporation.

© 1998 National Semiconductor Corporation

DS100239

.national.

Connection Diagrams

(Continued) Pin Names Description

Data Inputs Clock Pulse Input TRI-STATE Output Enable Input TRI-STATE Outputs

D0- D7 CP OE O0- O7

Functional Description

The ’ACQ/’ACTQ374 consists of eight edge-triggered flip-flops with individual D-type inputs and TRI-STATE true outputs. The buffered clock and buffered Output Enable are mon to all flip-flops. The eight flip-flops will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (CP) transition....